Improvements:

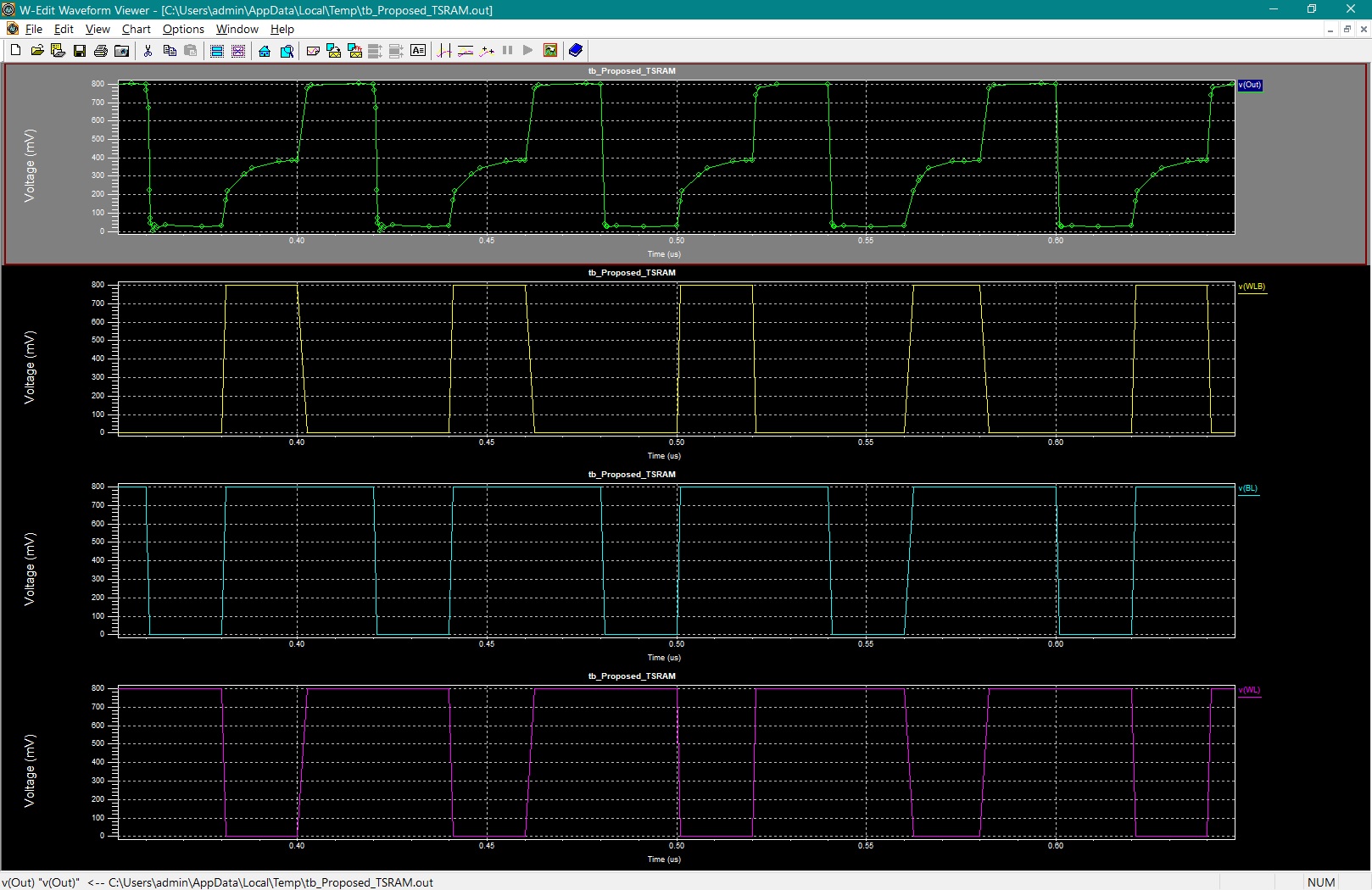

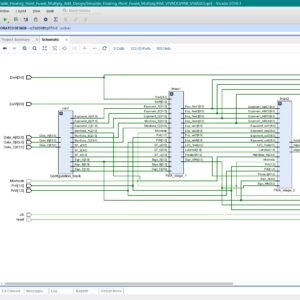

- To develop the Ternary Static Random Access Memory design using 22nm CMOS technology by Tanner EDA.

- To remodified the architecture 10T Ternary SRAM to 8T Ternary SRAM and proved the performance of area, delay and power in Tanner EDA.

Proposed abstract:

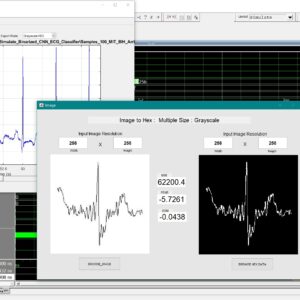

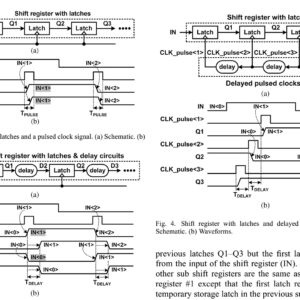

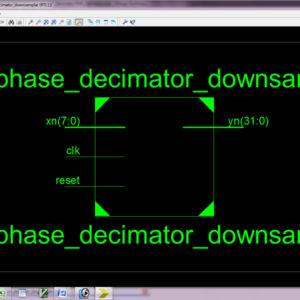

Ternary logic-based memory systems have gained growing importance in modern low-power computing applications such as Internet of Things (IoT), medical imaging, and portable electronic systems due to their ability to store and process more data per cell compared to conventional binary memories. The major advantages of ternary logic include reduced interconnection complexity, higher data density, and improved energy efficiency; however, these designs often face challenges of increased circuit area, poor noise margin stability, and higher power dissipation caused by voltage division networks and larger transistor counts. Existing Ternary Static Random-Access Memory (TSRAM) architectures such as 10T, 12T, 14T, and 16T cells show limitations in minimizing area and power while maintaining stability and speed. To overcome these issues, this work proposes a novel 8T Ternary SRAM cell designed and simulated using 22 nm CMOS technology in Tanner EDA. The proposed design eliminates redundant transistors and voltage division networks by introducing an optimized feedback-based latch structure that supports three stable logic levels (0, 1, and 2) with a single bit line configuration. This modification significantly reduces static and dynamic power consumption and achieves better stability compared to conventional ternary SRAMs. The novelty of the proposed design lies in its compact 8T configuration that offers improved area efficiency while maintaining low delay and strong data retention characteristics, making it suitable for embedded and IoT applications. Performance parameters such as read/write delay, power consumption, power-delay product (PDP), and static noise margin (SNM) are analysed and compared with existing designs through schematic and post-layout simulations using Tanner EDA tools. The results demonstrate that the proposed 8T TSRAM achieves superior energy efficiency and reduced area overhead, thereby offering a practical solution for next-generation high-density, low-power memory design.

Software Implementation:

- Modelsim & Xilinx

” Thanks for Visit this project Pages – Buy It Soon “

A Compact 8T Ternary SRAM Architecture for Low-Power Applications in 22 nm CMOS Technology

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200090465140,

IFSC CODE: HDFC0000407.