No products in the cart.

Return To ShopHDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200090465140,

IFSC CODE: HDFC0000407.

₹25,000.00 Original price was: ₹25,000.00.₹12,000.00Current price is: ₹12,000.00.

Source : Verilog HDL

Base paper abstract:

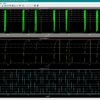

This paper presents two novel architectures to generate a number of quantized Gaussian noises. The first architecture exploits inversion through uniform segmentation, enabling a uniform look up table (LUT) splitting technique to efficiently generate quantized Gaussian noise while maintaining reasonable tail quality in Gaussian noise generation. The second architecture utilizes inversion through hierarchical segmentation and a probability-based LUT selection, significantly reducing the total LUT size while preserving the tail quality of the generated Gaussian noise. Both designs generate multiple uniform random numbers by cascading combinational circuits, which improves Gaussian noise generation efficiency compared to the conventional linear feedback shift register-based method. Compared to the previous architecture based on inversion through hierarchical segmentation, the proposed uniform segmentation architecture achieves a 6.02x improvement, when implemented on a field-programmable gate array device, in terms of throughput per configurable logic block, and the proposed hierarchical segmentation architecture achieves a 2.71x improvement.

List of the following materials will be included with the Downloaded Backup:

Objective of this work:

Proposed abstract:

Additive white Gaussian noise generation is widely used in wireless communication testing, BER evaluation of digital modulation schemes, channel emulation, and signal-processing system validation. Hardware realization of Gaussian noise generators enables high-speed and real-time operation compared to software simulation; however, conventional inversion-based architectures require large LUT memory, complex ICDF computation, and multiple leading-one detectors when parallel outputs are needed. Quantized Gaussian noise generation (QGNG) reduces precision requirements and hardware cost, but parallel implementations still suffer from LUT replication and increased logic usage. Uniform segmentation offers lower complexity but may weaken tail behavior, whereas hierarchical segmentation provides better statistical accuracy at the cost of higher hardware overhead. To address these challenges, this work presents three FPGA-based architectures described and implemented in Verilog HDL and synthesized on a Xilinx Virtex-5 device. The first architecture is a baseline QGNG using conventional hierarchical segmentation. The second architecture employs uniform segmentation with LUT splitting and output shuffling to reduce memory duplication and eliminate costly segment-selection logic. The third architecture proposes an optimized hierarchical segmentation with probability-based LUT sharing and a modified unrolled Galois LFSR capable of generating multiple uniform random numbers per cycle without multiple URNG blocks. Compared with the baseline design, the proposed architectures significantly reduce LUT and flip-flop utilization while maintaining high throughput and parallel generation capability. Statistical validation through PMF matching, chi-square tests, autocorrelation analysis, and BER evaluation confirms that both proposed designs preserve sufficient Gaussian characteristics and tail accuracy. Experimental synthesis results demonstrate improved throughput-per-CLB and reduced area and power consumption, proving that the proposed FPGA implementations provide scalable, low-complexity, and statistically reliable parallel QGNG solutions for communication and signal-processing systems.

” Thanks for Visit this project Pages – Buy It Soon “

Payment Method :

HDFC BANK ACCOUNT:

₹12,000.00 Original price was: ₹12,000.00.₹6,000.00Current price is: ₹6,000.00.

₹20,000.00 Original price was: ₹20,000.00.₹10,000.00Current price is: ₹10,000.00.

Copyright © 2026 Nxfee Innovation.