Improvements:

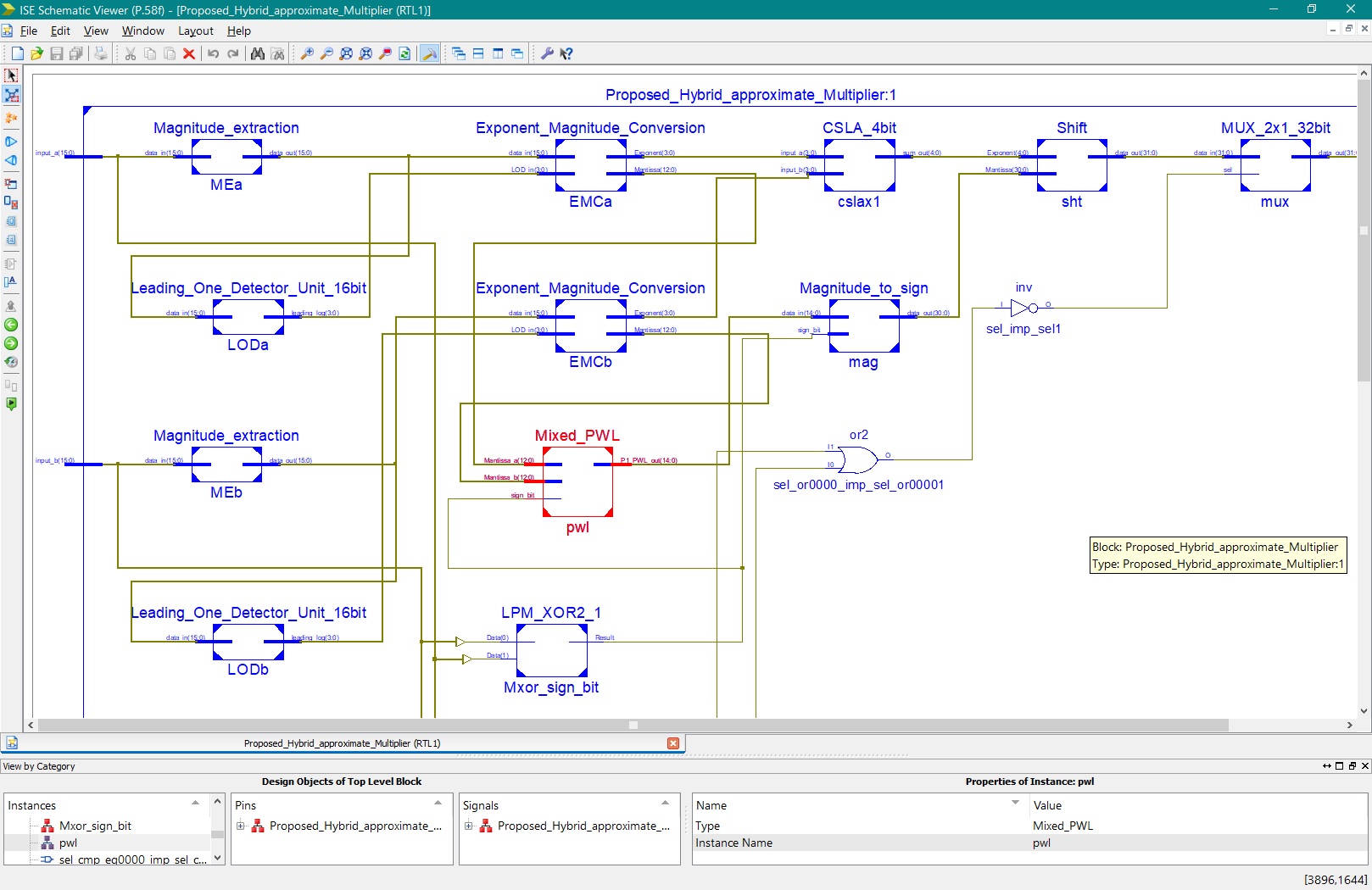

- To design the Hybrid approximate multiplier using carry select adder which is implemented using the XOR MUX based full adder and comparing in terms of the area, delay, power consumption and in order to reduce the latency and complexity.

Proposed abstract:

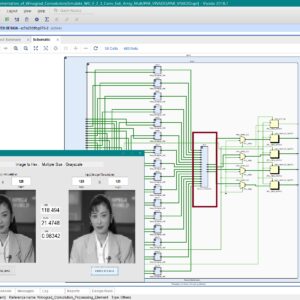

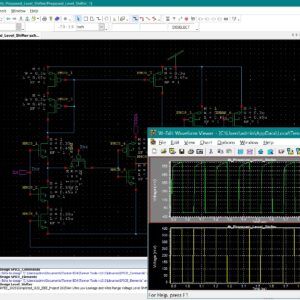

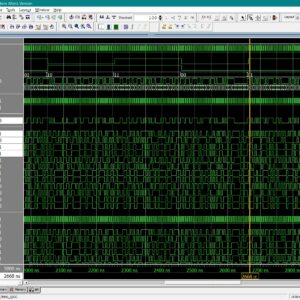

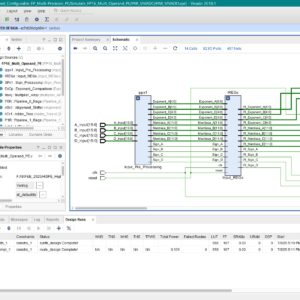

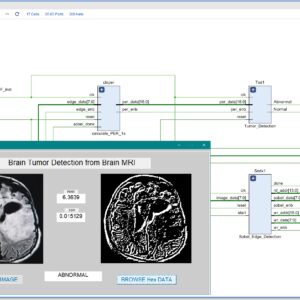

Digital signal processing, image processing, and neural network acceleration widely rely on high-speed multiplication, where approximate computing has emerged as an effective approach to improve energy efficiency and throughput. Approximate multipliers offer clear advantages in terms of reduced power consumption, smaller area, and faster operation; however, they also introduce challenges such as unbalanced error distribution, increased latency in accumulation stages, and performance degradation due to inefficient adder structures. The primary problem addressed in this work is the delay and hardware complexity caused by conventional adders used in hybrid approximate multiplier architectures, which limits their effectiveness on FPGA platforms. Existing approaches mainly focus on approximation at the arithmetic level, such as logarithmic or partial-product-based designs, but often neglect optimization of the carry propagation and accumulation logic, resulting in suboptimal delay and power performance. To overcome these limitations, this work proposes a hybrid approximate multiplier architecture that integrates a carry select adder implemented using an XOR–MUX-based full adder to reduce carry propagation delay and overall circuit complexity. The key novelty of the proposed design lies in combining approximation-aware multiplication with a low-latency, hardware-efficient adder structure, enabling improved speed without significantly affecting computational accuracy. The proposed architecture supports signed arithmetic operations and is well suited for error-tolerant applications in FPGA-based systems. The design is described using Verilog HDL, functionally verified in ModelSim, and synthesized on a Xilinx Virtex-5 FPGA platform. Performance evaluation is carried out in terms of lookup table utilization, slice registers, critical-path delay, and power consumption, demonstrating noticeable improvements over existing hybrid approximate multiplier designs, thereby ensuring enhanced performance, energy efficiency, and reliable operation.

Software Implementation:

- Modelsim

- Xilinx

” Thanks for Visit this project Pages – Buy It Soon “

Design of an Efficient Hybrid Approximate Multiplier Employing XOR-MUX-Based Carry Select Adder for Reduced Latency and Complexity

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200090465140,

IFSC CODE: HDFC0000407.