Proposed Abstract:

In modern cryptographic systems, the reliable generation of high-quality pseudo-random numbers is critical for ensuring data integrity and confidentiality, particularly in resource-constrained environments such as IoT devices, embedded systems, and sensor networks. While existing cryptographically secure pseudo-random number generators (CSPRNGs) based on algorithms like AES, DES, or SHA offer robust security, they often struggle with challenges like high resource demands, power consumption, and complexity, making them less suitable for low-power, compact applications.

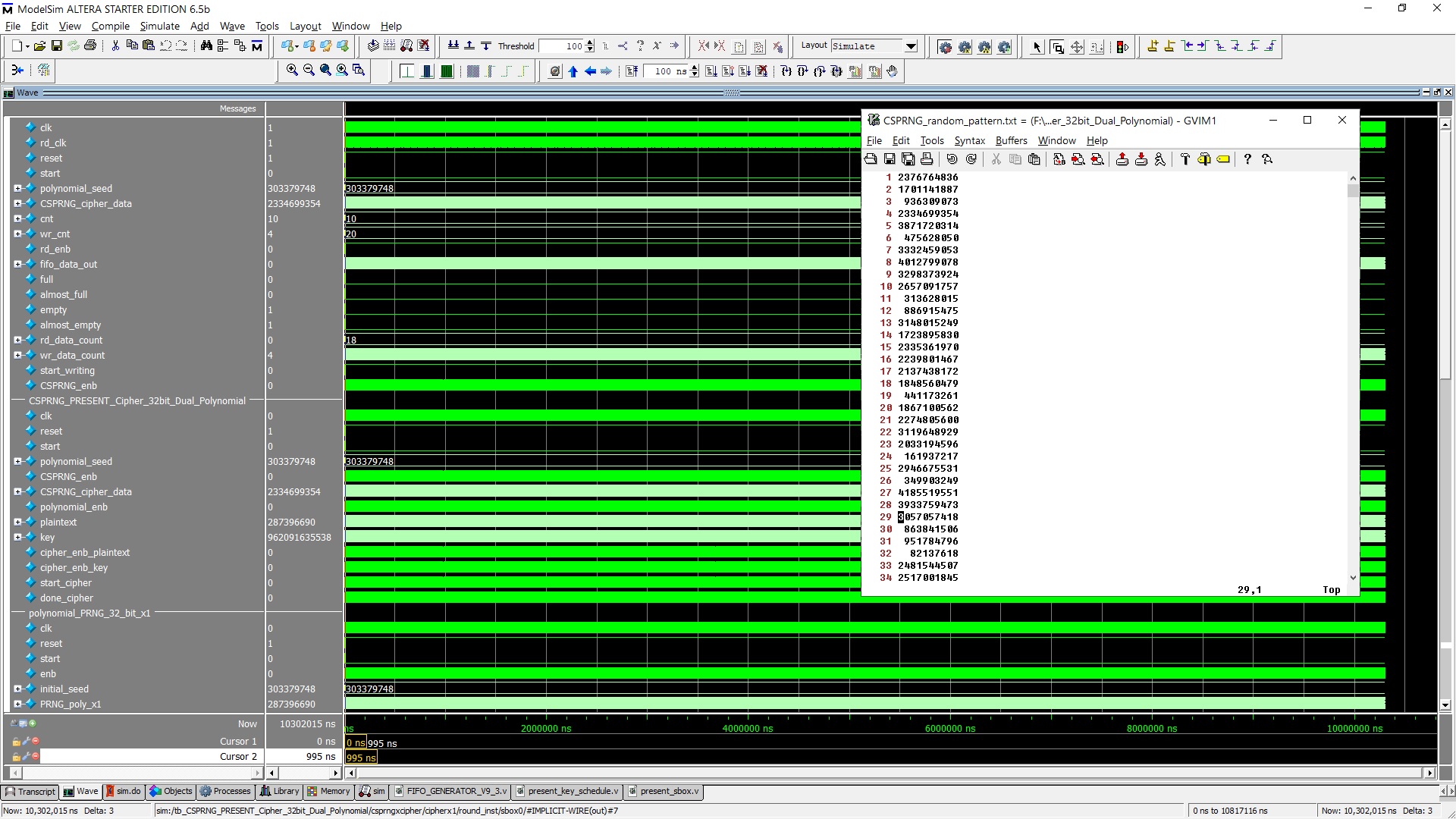

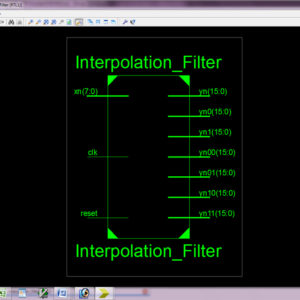

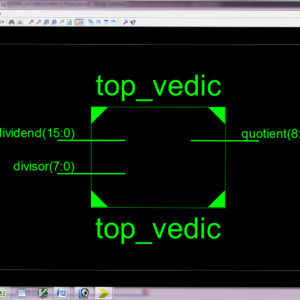

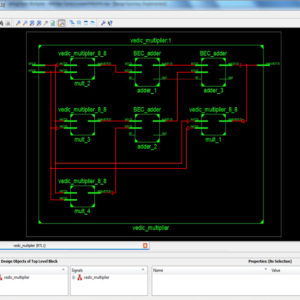

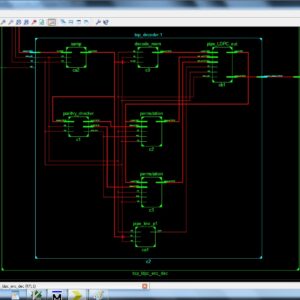

This paper presents an innovative 32-bit CSPRNG architecture that combines the lightweight PRESENT block cipher with a dual polynomial-based pseudo-random number generator (PRNG) scheme. The proposed design incorporates two distinct polynomial PRNGs: one for generating the plaintext input and the other for producing the key input to the PRESENT cipher. This dual-PRNG strategy not only prevents repetitive random patterns but also significantly enhances the precision and randomness quality, bolstering resistance to cryptanalytic attacks.

The architecture is implemented in Verilog HDL and synthesized on the Xilinx Virtex-5 FPGA, a platform that strikes a balance between performance and efficiency. Comprehensive evaluations of the proposed system highlight key performance metrics such as area utilization, critical path delay, and power consumption. Results demonstrate that this approach achieves superior resource efficiency and reduced power consumption while maintaining or exceeding the security standards of more complex algorithms like AES and SHA.

Additionally, the theoretical foundations of dual polynomial PRNGs are explored, showcasing their ability to mitigate pattern repetition and enhance entropy and unpredictability. This feature is especially beneficial for applications requiring long-term operation without re-seeding, thereby extending the operational lifespan of secure systems in the field.

In summary, the proposed CSPRNG architecture represents a significant step forward in the design of secure and efficient random number generators, tailored for applications where both security and resource efficiency are critical. The integration of dual polynomial PRNGs with the PRESENT cipher establishes this work as a valuable contribution to cryptographic hardware design, with direct implications for advancing secure, low-power technologies such as IoT, RFID, and distributed network applications.

Software Implementation:

- Modelsim

- Xilinx

” Thanks for Visit this project Pages – Buy It Soon “

Design and Implementation of 32-bit CSPRNG using the PRESENT cipher with Dual Polynomial PRNG for Enhanced Randomness and Precision

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200090465140,

IFSC CODE: HDFC0000407.