Proposed Title:

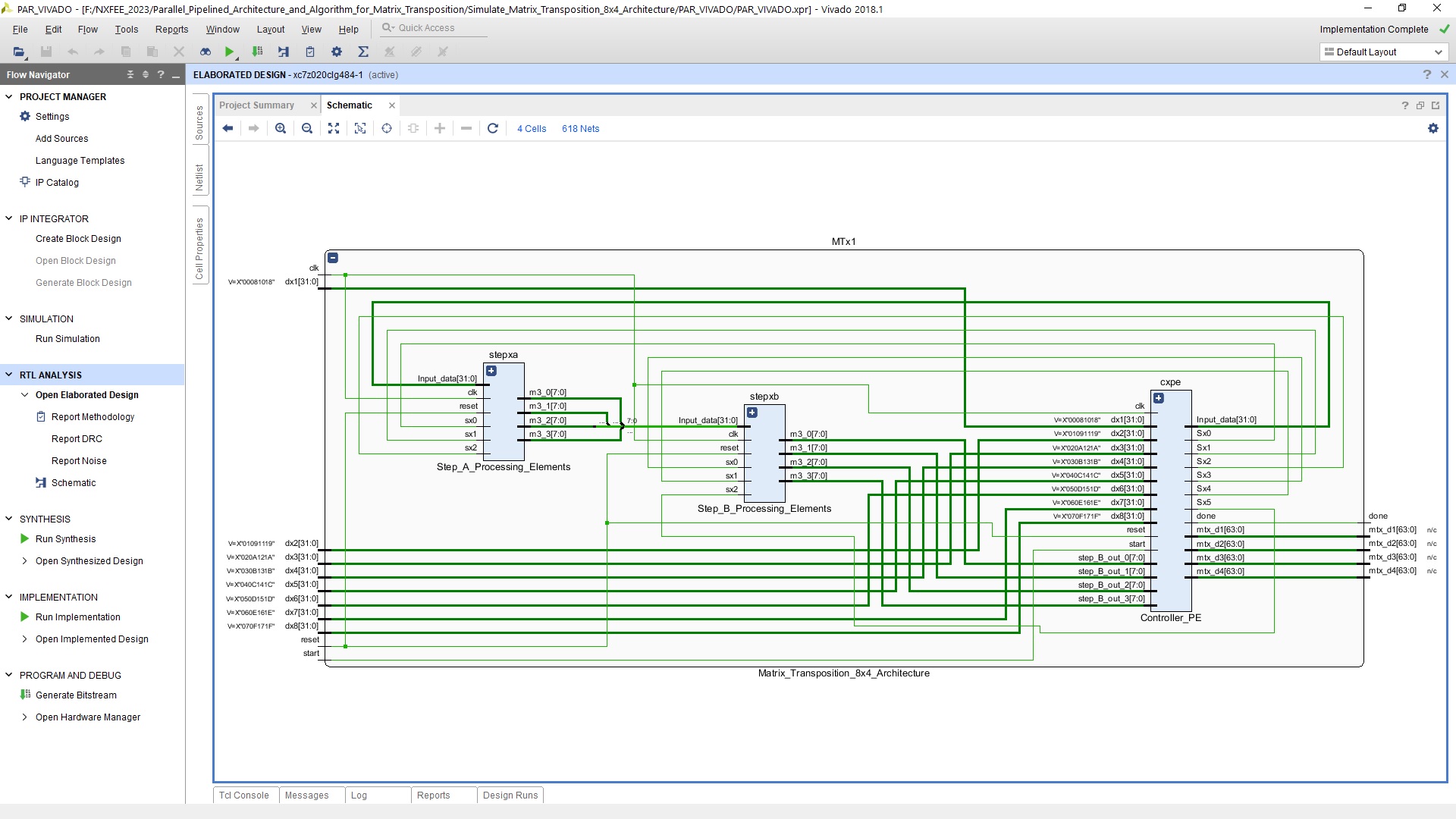

FPGA implementation of pipelined 3 and 4 parallel architecture in various matrix transposition sizes

Improvement of this project :

To design the 3 parallel architecture of 9×6 matrix transposition architecture and prove the performance of area, delay and power.

To design the proposed parallel multi-path architecture of 8×4 matrix transposition, and novelty architecture of 8×8 matrix transposition.

This three different architecture will be compared and proved the performance of area, delay and power.

Software Implementation:

- Modelsim

- Xilinx

Proposed System:

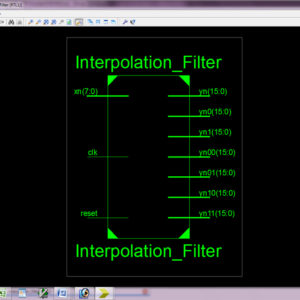

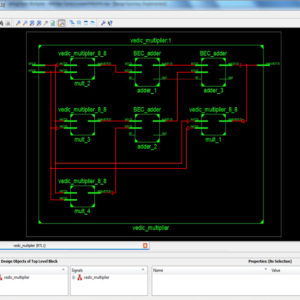

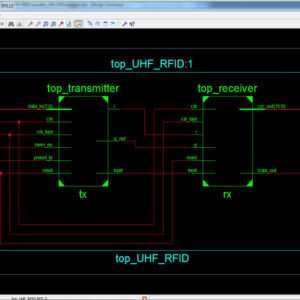

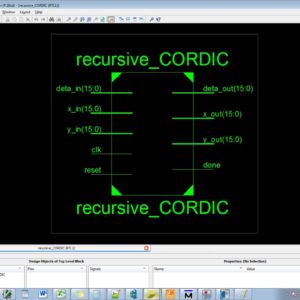

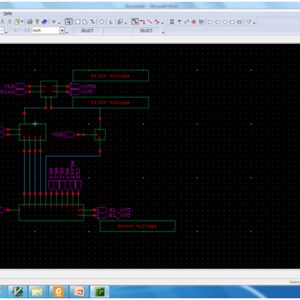

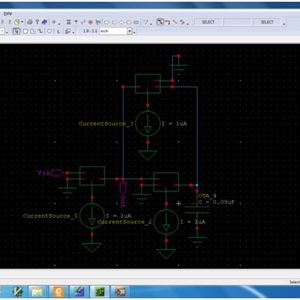

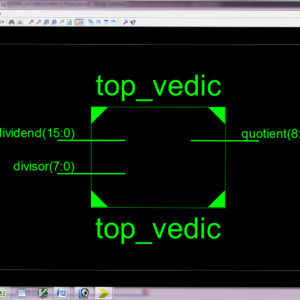

This research presents FPGA implementations of pipelined 3 and 4 parallel architectures, configured for matrix transposition sizes of 9×6, 8×4, and 8×8. Leveraging parallelism and pipelining, the architectures are designed to enhance computational throughput and efficiency. Through careful resource allocation and the integration of pipeline registers, concurrent processing of multiple stages is achieved, optimizing overall performance. The existing architecture consists of a series of identical cascaded basic swap circuits, whose stages are determined by the corresponding algorithm and can be controlled via a set of counters. Notably, the existing architecture will occupy more logic size and power consumption. Moreover, the proposed algorithm and architecture could be easily extended to N-parallel implementations for matrix transposition. This architecture supports matrices whose rows and columns are integer multiples; it is mainly used for radix-2s butterfly algorithms using matrix transpositions. Comparative evaluations against state of the art architecture and demonstrate the superiority of the proposed FPGA-based parallel architectures over conventional methods. This study underscores the versatility and scalability of FPGA implementations for parallel processing across various computational tasks. The proposed architecture designed in Verilog HDL and synthesized using Xilinx Vertex-5 FPGA, and compared the parameters in terms of area, delay and power.

” Thanks for Visit this project Pages – Buy It Soon “

Parallel Pipelined Architecture and Algorithm for Matrix Transposition Using Registers

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.