Proposed Title :

Low Power, High performance 32-bit Area-efficient design for Fixed Width Adder Tree

Improvement of this Project:

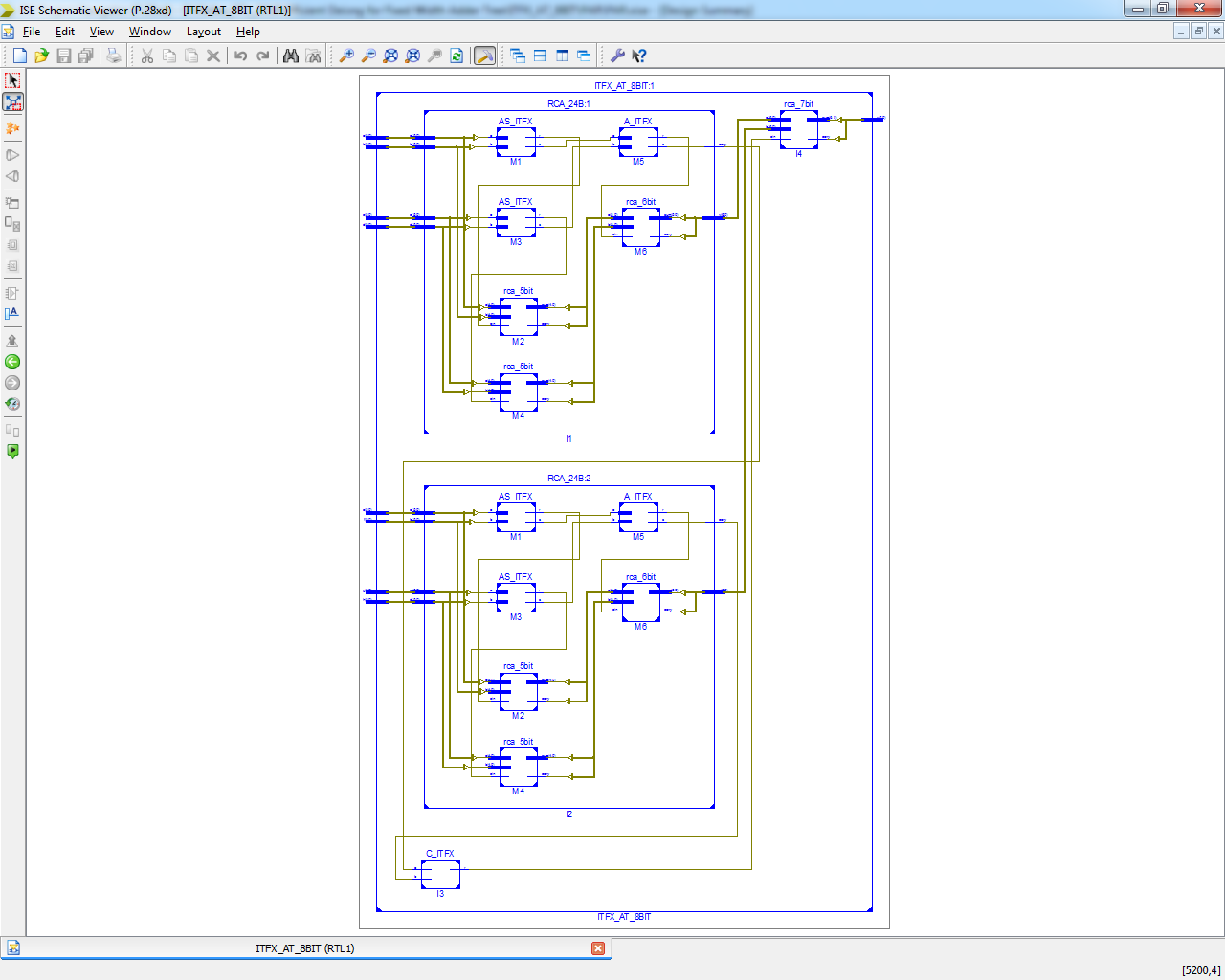

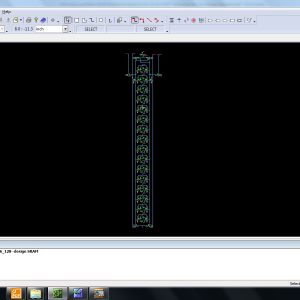

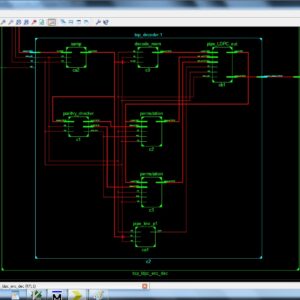

Implement Fixed with Adder Tree at 32-bit, 16-bit and 8-bit and finally proved the comparison of Area, delay and power,.

Software implementation:

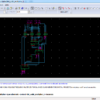

- Modelsim & Xilinx 14.2

Proposed System:

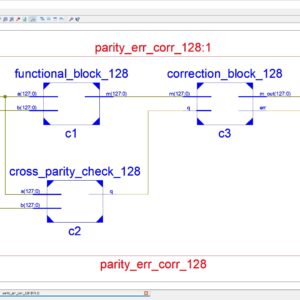

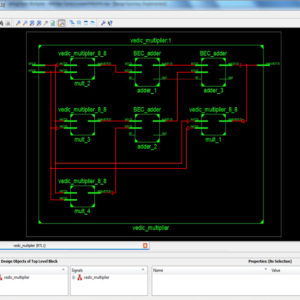

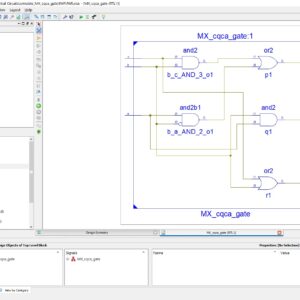

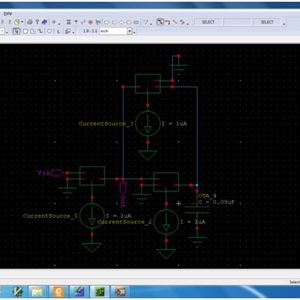

The Adder plays a vital role in many applications of VLSI design. The Adder-tree (AT) commonly used in parallel designs of inner product computation and matrix-vector multiplication. Conventionally, fixed-width adder-tree (AT) design is obtained from the full-width AT design by employing direct or post-truncation. But, both of these methods are not provide a efficient design for adder tree. This paper proposes the novel design implementation in order to obtain the fixed width adder Tree design using the truncated input. The truncation error is compensated by the bias estimation formula which is based on the probabilistic approach. Based on the proposed scheme, three separate fixed width Adder tree includes the vector sizes of 8, 16 and 32 are designed. Thus, the proposed fixed width adder tree design for input vector sizes 8, 16 and 32 offers the better area delay product (ADP) and also has a better efficiency when compared to the existing fixed-width adder tree. Further, we observed that Walsh-Hadamard transform based on proposed adder design reconstruct higher-texture images with higher PSNR and moderate-texture images with almost the same PSNR compared to those obtained from the existing fixed-width adder designs. Finally, the fixed width adder tree design is implemented in the VHDL and synthesized in the XILINX and compared in terms of area, power and delay reports.

Advantages:

- Proposed system uses truncated input for efficient fixed width adder tree design.

- Better Area Delay Product (ADP).

- Using, bias estimation formula based on probabilistic approach for compensating the truncation error.

” Thanks for Visit this project Pages – Buy It Soon “

Efficient Design for Fixed-Width Adder-Tree

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link