Proposed Title:

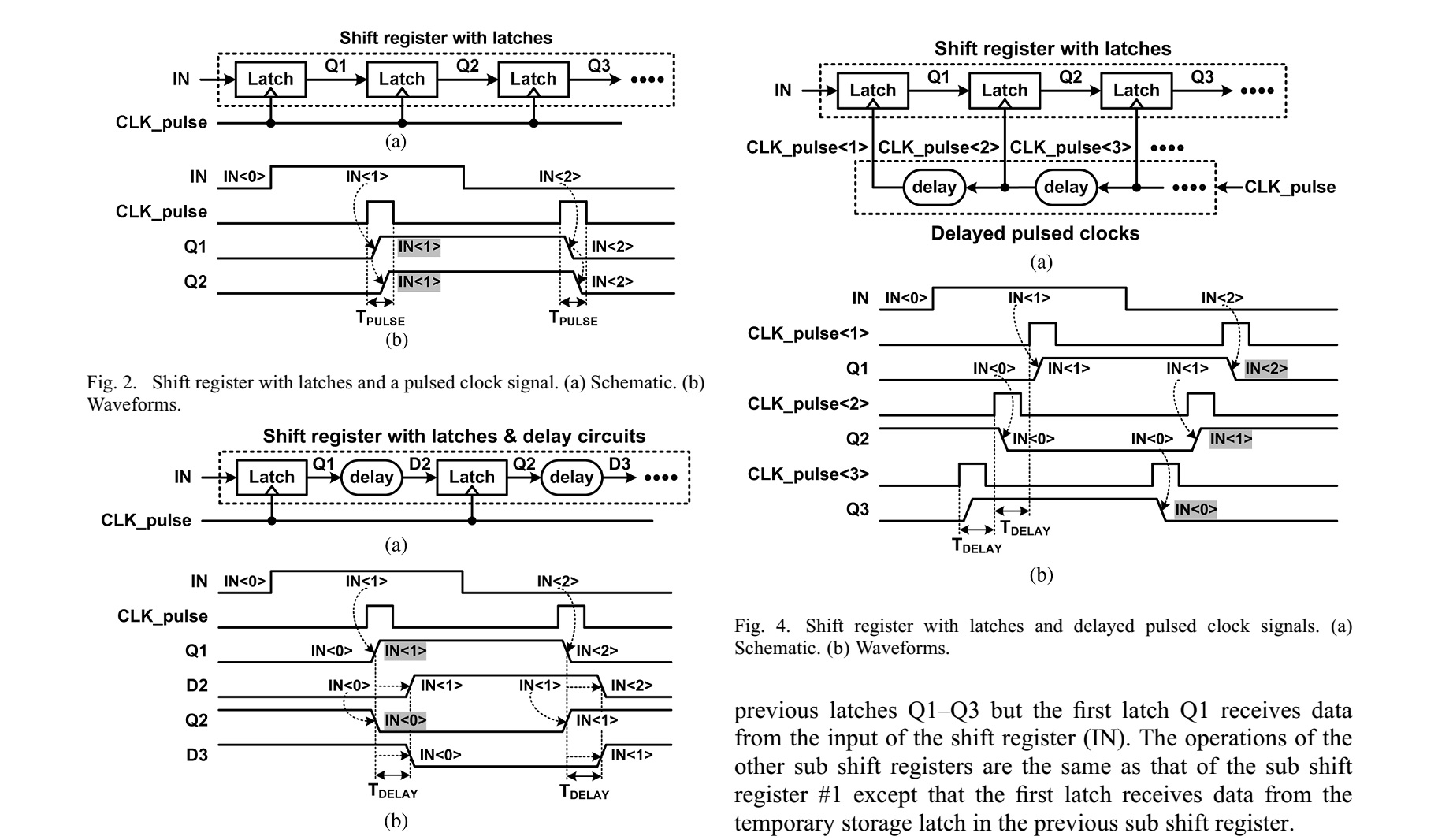

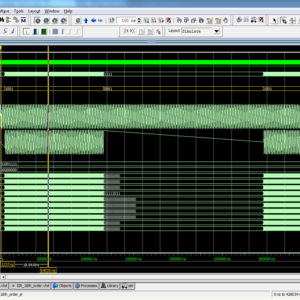

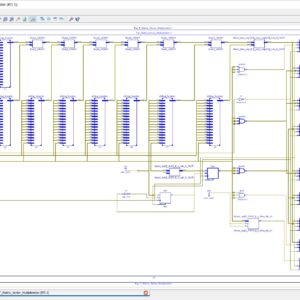

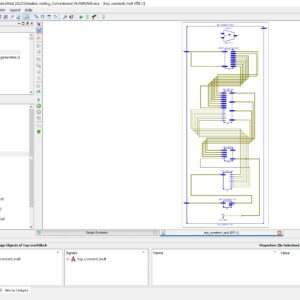

Low Power and Area Efficient Shift Register with CMOS 130nm using Pulsed Latches Flip Flop and Ring counters

Proposed System:

- To Reduced the Power consumption as per the comparison of this base paper.

Advantages:

- Reduced the Power

- Increases the speed

Software used:

- Tanner EDA Tool v13

Reviews

There are no reviews yet.