Proposed Title :

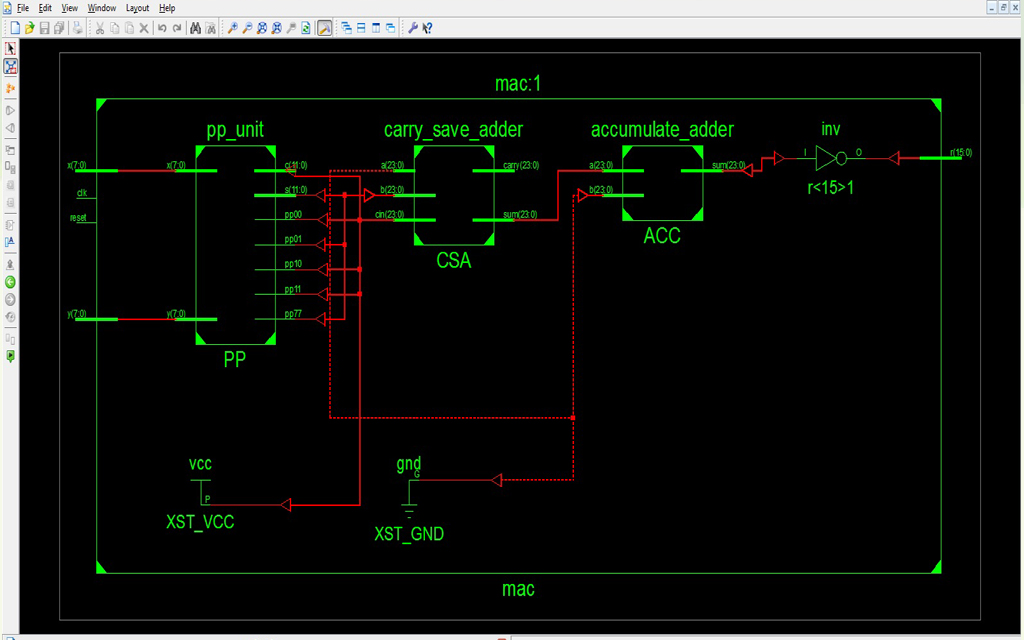

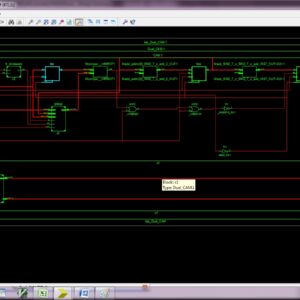

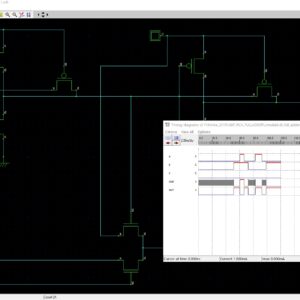

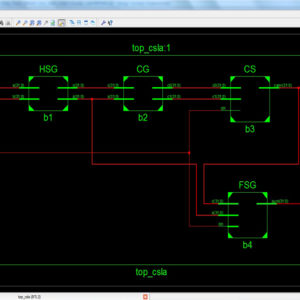

FPGA Implementation of Low Area and Low Power Compressor based MAC Architecture for DSP Application

Proposed System:

- Reduced the power consumption compared to the existing architecture

- Simplified the area size using VHDL technique

Advantages:

- Reduce the power level

- Reduced the area size

- Fastest Multiplication

Reviews

There are no reviews yet.