Proposed Title :

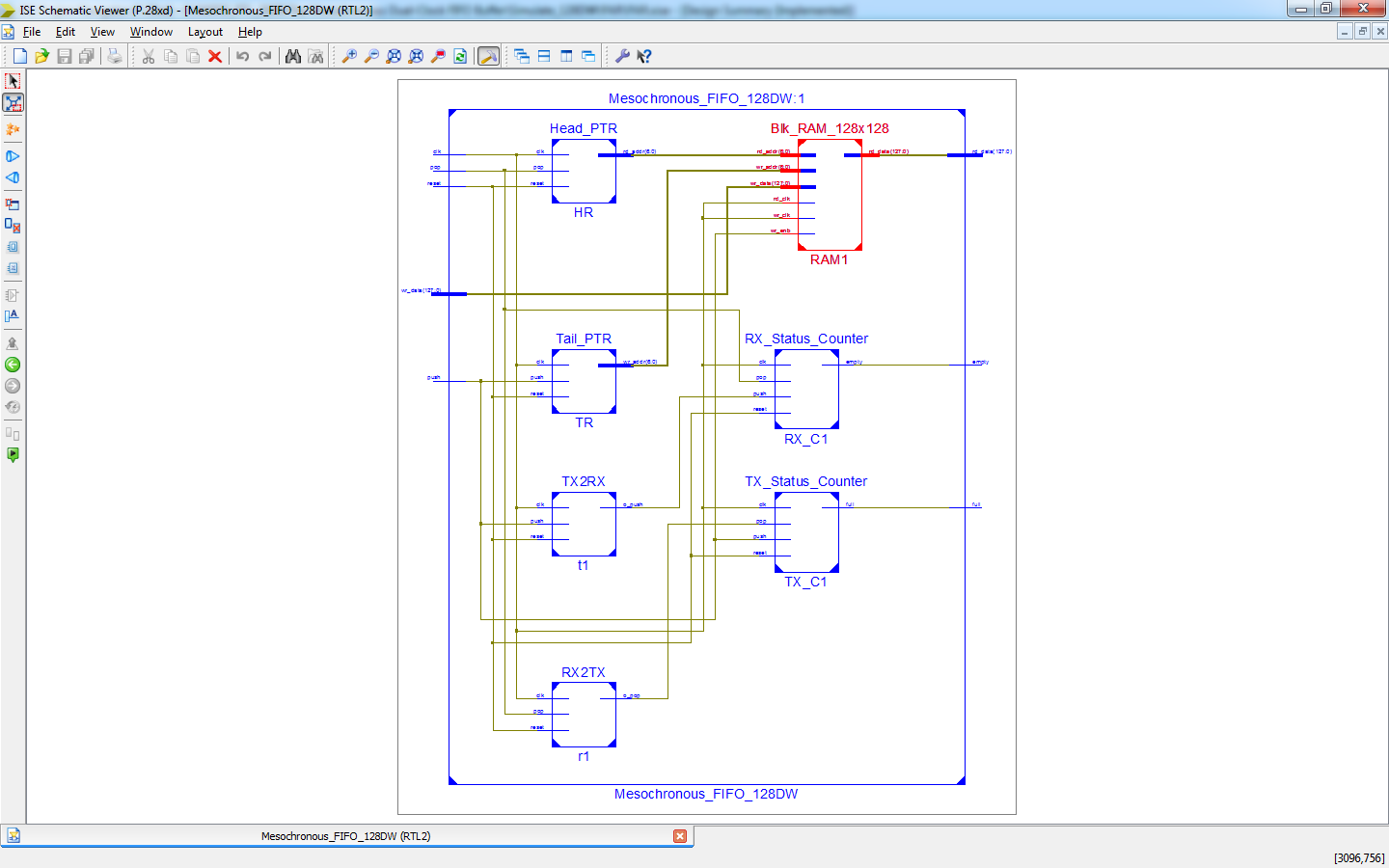

FPGA Implementation of Dual Clock 4-Slot Mesochronous FIFO Buffer using 128 Data Width

Improvement of this Project:

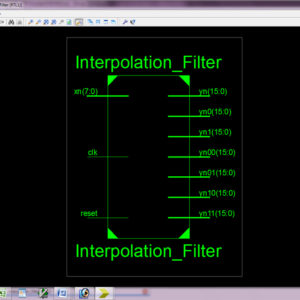

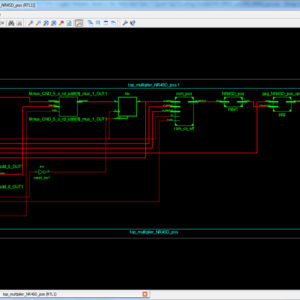

Increases the data width up to 128 bits, and prove the performance with existing data width 64 bits.

Designed 4-Slot deep structure at 128 data width.

Software implementation:

- Xilinx 14.2

Proposed System:

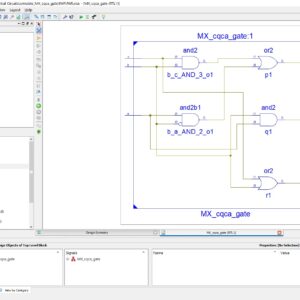

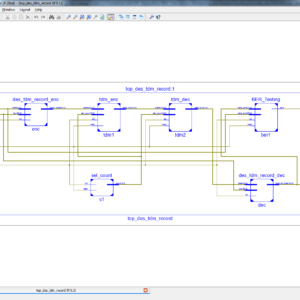

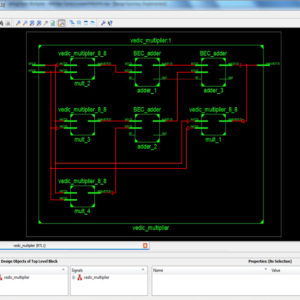

Completely synchronous clocking is replaced by more relaxed clocking systems, such as mesochronous clocking, to improve device composability and promote timing elimination. In this framework, the modules receive the same clock signal at both ends of the mesochronous interface, while working under the same clock frequency, but the edges of the arriving clock signals can have an undefined phase relationship. In such instances, when transmitting data through modules, clock synchronisation is required. In this paper, we introduce a new mesochronous first-input-first-output (FIFO) dual-clock buffer that can accommodate both clock synchronisation and temporary data storage by implicitly synchronising data while specifically synchronising only the flow-control signals. And when the transmitter and the receiver are separated by a long connexion whose delay cannot match into the target operating frequency, the proposed design can work correctly. The suggested mesochronous FIFO can be expanded in such situations to support multicycle connexion delays in a modular way and with limited adjustments to the baseline architecture. The new architecture is seen to deliver a significantly lower cost implementation as compared to the other state-of-the-art dual-clock mesochronous FIFO designs. Finally this work developed at 128 and 64 data width and proved the performance of area, delay and power consumptions.

” Thanks for Visit this project Pages – Buy It Soon “

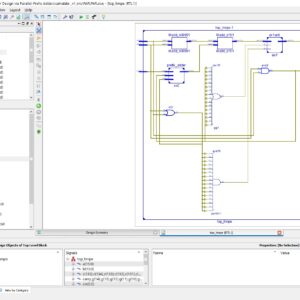

The Mesochronous Dual-Clock FIFO Buffer

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.