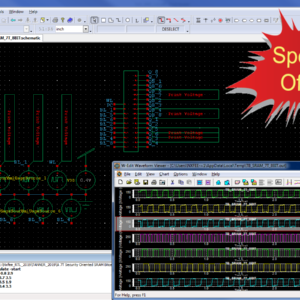

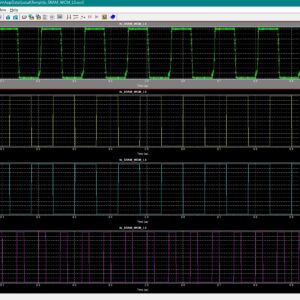

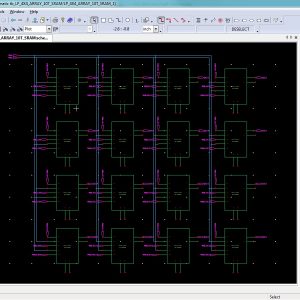

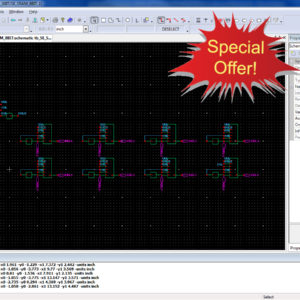

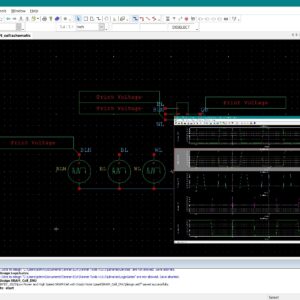

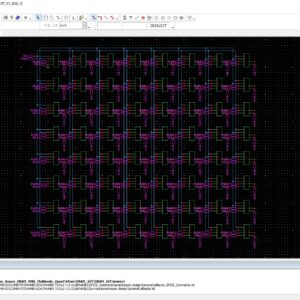

A 7T Security Oriented SRAM Bitcell

Abstract:

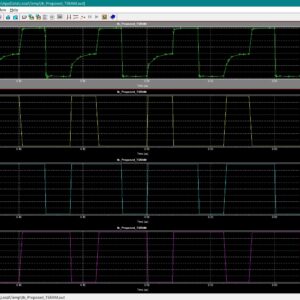

Power analysis (PA) attacks have become a serious threat to security systems by enabling secret data extraction through the analysis of the current consumed by the power supply of the system. Embedded memories, often implemented with six-transistor (6T) static random access memory (SRAM) cells, serve as a key component in many of these systems. However, conventional SRAM cells are prone to side-channel power analysis attacks due to the correlation between their current characteristics and written data. To provide resiliency to these types of attacks, we propose a security-oriented 7T SRAM cell, which incorporates an additional transistor to the original 6T SRAM implementation and a two-phase write operation, which significantly reduces the correlation between the stored data and the power consumption during write operations. The proposed 7T SRAM cell was implemented in a 28 nm technology and demonstrates over 1000× lower write energy standard deviation between write ‘1’ and ‘0’ operations compared to a conventional 6T SRAM. In addition, the proposed cell has a 39%–53% write energy reduction and a 19%–38% reduced write delay compared to other power analysis resistant SRAM cells.

List of the following materials will be included with the Downloaded Backup:A Fast and Energy-Efficient Level Shifter with Complementary Output Buffer for Energy-Constrained Systems

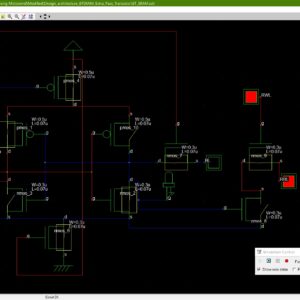

This brief presents a 55-nm level shifter (LS) that enables wide voltage range conversion from 80 mV to 1.2 V with high energy efficiency and fast transition speed. The proposed design incorporates a complementary output buffer and an assist discharge path to suppress the short-circuit current and enhance the transition speed. A multi threshold transistor strategy is adopted to expand the input range and reduce static power. Measurement results across 15 samples demonstrate robust subthreshold performance with 4.4-ns transition delay and 49.1-fJ/transition energy during 0.3–1.2-V conversion at 1 MHz. The measured average minimum convertible input voltages are 80 and 139 mV at input frequencies of 50 kHz and 1 MHz, respectively. The compact layout occupies only 7.96 µm 2. Compared to the best benchmarked prior work, the proposed LS achieves 33.8% improvement in energy-delay metrics, making it a highly efficient and scalable solution for energy constrained systems and the Internet of Things (IoT). Index Terms: Current mirror (CM), dual supply, level shifter (LS), low power, subthreshold.

List of the following materials will be included with the Downloaded Backup:A Reliable Low Standby Power 10T SRAM Cell With Expanded Static Noise Margins

Abstract:

This paper explores a low standby power 10T (LP10T) SRAM cell with high read stability and write-ability (RSNM/WSNM/WM). The proposed LP10T SRAM cell uses a strong cross-coupled structure consisting standard inverter with a stacked transistor and Schmitt-trigger inverter with a double-length pull-up transistor. This along with the read path separated from true internal storage nodes eliminates the read-disturbance. Furthermore, it performs its write operation in pseudo differential form through write bit line and control signal with a write-assist technique. To estimate the proposed LP10T SRAM cell’s performance, it is compared with some state-of-the-art SRAM cells using HSPICE in 16-nm CMOS predictive technology model at 0.7 V supply voltage under harsh manufacturing process, voltage, and temperature variations. The proposed SRAM cell offers 4.65X/1.57X/1.46X improvement in RSNM/WSNM/WM and 4.40X/1.69X narrower spread in RSNM/WM compared to the conventional 6T SRAM cell. Furthermore, it shows 1.26X/1.08X/1.01X higher RSNM/WSNM/WM and 1.71X/1.25X tighter/wider spread in RSNM/WM compared to the best studied SRAM cells. The proposed SRAM cell indicates 74.48%/1.41% higher/lower read/write delay compared to the 6T SRAM cell. Moreover, it exhibits the third-(second-) best read (write) dynamic power, consuming 29.69% (26.87%) lower than the 6T SRAM cell. The leakage power is minimized by the proposed design, which is 37.35% and 12.08% lower than that of the 6T and best studied cells, respectively. Nonetheless, the proposed LP10T SRAM cell occupies 1.313X higher area compared to the 6T SRAM cell.

List of the following materials will be included with the Downloaded Backup:Column-Selection-Enabled 10T SRAM Utilizing Shared Diff-VDD Write and Dropped-VDD Read for Power Reduction

Abstract:

A non-destructive column-selection-enabled 10T SRAM for aggressive power reduction is presented in this brief. It frees a half-selected behavior by exploiting the bit line-shared data-aware write scheme. The differential-VDD (Diff-VDD) technique is adopted to improve the write ability of the design. In addition, its decoupled read bit lines are given permission to be charged and discharged depending on the stored data bits. In combination with the proposed dropped-VDD biasing, it achieves the significant power reduction. The experimental results show that the proposed design provides the 3.3× improvement in the write margin compared with the standard Diff-10T SRAM. A 5.5-kb 10T SRAM in a 65-nm CMOS process has a total power of 51.25 µW and a leakage power of 41.8 µW when operating at 6.25 MHz at 0.5 V, achieving 56.3% reduction in dynamic power and 32.1% reduction in leakage power compared with the previous single-ended 10T SRAM.

List of the following materials will be included with the Downloaded Backup:Energy-Efficient Buffer-Based Ternary SRAM Cell With Application to Image Processing

Base Paper Abstract:

This paper presents a design of a variation-resilient and energy-efficient ternary memory cell (TSRAM) suited for power-demanding internet-of-things (IoT) applications that run on batteries. The TSRAM cell utilizes a latch composed of an efficient ternary buffer (TBUF) with positive feedback, a single bit line, and a transmission gate for switching access, with an overall area only about 39% more than binary 6T SRAM. The threshold voltage (Vth) tuning of carbon nanotube field-effect transistor (CNTFET) devices has been explored to achieve the three storage levels. Simulations were conducted using the standard Stanford 32-nm CNTFET model file in the Synopsis HSPICE simulator. The projected design offers substantial reductions of 54.94% in real power, 67.06% in write power, and 21.59% in area compared to the best buffer-based TSRAM designs. These power savings are achieved by minimizing the transistor count and eliminating any direct current path between VDD and ground in the TBUF design for getting logic ‘1’. Furthermore, the proposed design demonstrates the highest logic ‘1’ static noise margin (SNM1) and shows resilience to process, voltage, and temperature (PVT) variations. The TSRAM electrical quality matrix (TEQM), a crucial figure of merit, indicates the superior performance of the proposed design for IoT applications. The study was further extended to conduct simulations and report the performance metrics of the proposed TSRAM array. Ultimately, to evaluate the real-world application of the triple memory structures, the pixel-by-pixel storage process of a grayscale image with three-value data content is performed based on a hardware algorithm. The obtained results demonstrate that the proposed TSRAM architecture has about a 26.3% improvement in hardware performance compared to its highest performing counterpart scheme.

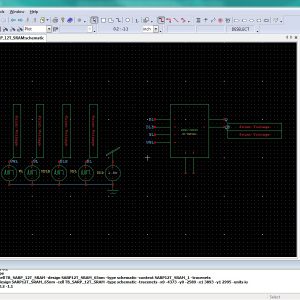

List of the following materials will be included with the Downloaded Backup:ER-TCAM: A Soft-Error-Resilient SRAM-Based Ternary Content-Addressable Memory for FPGAs

Abstract:

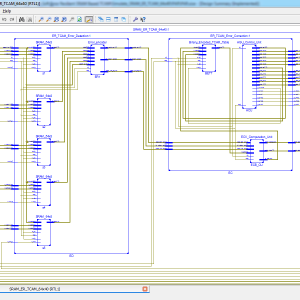

Static random access memory (SRAM)-based ternary content-addressable memory (TCAM) on field-programmable gate arrays (FPGAs) is used for packet classification in software-defined networking (SDN) and Open Flow applications. SRAMs implementing TCAM contents constitute the major part of a TCAM design on FPGAs, which are vulnerable to soft errors. The protection of SRAM-based TCAMs against soft errors is challenging without compromising critical path delay and maintaining a high search performance. This brief presents a low cost and low-response-time technique for the protection of SRAM-based TCAMs. This technique uses simple, single-bit parity for fault detection which has a minimal critical path overhead. This technique exploits the binary-encoded TCAM table maintained in SRAM-based TCAMs for update purposes to implement a low-response-time error-correction mechanism at low cost. The error-correction process is carried out in the background, allowing lookup operations to be performed simultaneously, thus maintaining a high search performance. The proposed technique provides protection against soft errors with a response time of 293 ns, whereas maintaining a search rate of 222 million searches per second on a 1024 × 40 size TCAM on Artix-7 FPGA.

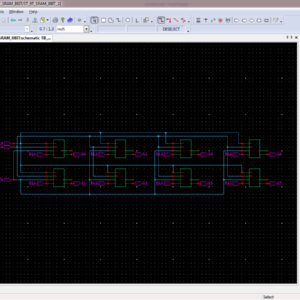

List of the following materials will be included with the Downloaded Backup:Full-Array Boolean Logic CIM Macro with Self-Recycling 10T-SRAM Cell for AES Systems

Base Paper Abstract:

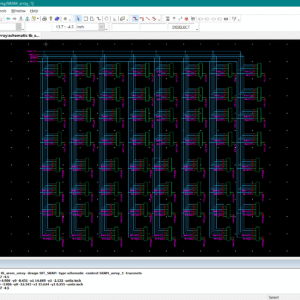

Computing in memory (CIM), which alleviates the need to transfer a large amount of data between processor and memory, significantly reducing latency and energy consumption, is a promising new computing architecture for addressing the von Neumann bottleneck problem. This article proposes a CIM array structure composed of self-recycling 10T static random access memory (SRAM) cells, which can realize orthogonal data writing, and multiple Boolean logical operations for the entire array. The self-recycling and full-array activation characteristics are extremely suitable for accelerating diverse data processing algorithms such as the Advanced Encryption Standard (AES). A 4-kb SRAM is implemented in 55-nm CMOS technology to verify the effectiveness of the design. Compared with other state-of-threat architectures, the throughput and the operating frequency of the proposed CIM macro are increased to 843 GOPS/kb (2.64×) and 823.7 MHz (2.6×), respectively. The energy efficiency reaches 246.9 TOPS/W. When applied to the AES, the energy consumption is 35.77% less than the digital CIM architecture that is not self-recycling.

List of the following materials will be included with the Downloaded Backup:Low voltage high speed 8T SRAM cell for ultra-low power applications

Proposed Abstract:

The usage of portable devices increasing rapidly in the modern life has led us to focus our attention to increase the performance of the SRAM circuits, especially for low power applications. Basically in Six-Transistor (6T) SRAM cell either read or write operation can be performed at a time whereas, in 7T SRAM cell using single ended write operation and single ended read operation both write and read operations will be accomplished simultaneously at a time respectively. When it comes to operate in sub threshold region, single ended read operation will be degraded severely and single ended write operation will be severely degraded in terms of write-ability at lower voltages. To encounter these complications, an eight transistor SRAM cell is proposed. It performs single ended read operation and single ended write operation together even at sub threshold region down to 0.1V with improved read-ability using read assist and improved dynamic write-ability which helps in reducing the consumption of power by attaining a lower data retention voltage point. To reduce the total power consumption in the circuits, two extra access transistors are used in 8T SRAM cell which also helps in reducing the overall delay.

List of the following materials will be included with the Downloaded Backup:Low-Power and High-Speed SRAM Cells With Double-Node Upset Self-Recovery for Reliable Applications

Transistor sizing and spacing are constantly decreasing due to the continuous advancement of CMOS technology. The charge of the sensitive nodes in the static random access memory (SRAM) cell gradually decreases, making the SRAM cell more and more sensitive to soft errors, such as single node upsets (SNUs) and double node upsets (DNUs). Therefore, two types of radiation-hardened SRAM cells are proposed in this article. First, a low-power DNU self-recovery S6P8N cell is proposed. This cell can realize SNU self-recovery from all sensitive nodes as well as realize partial DNUs self-recovery and has low-power consumption overhead. Second, we propose a high-speed DNU self-recovery S8P6N cell, which has a soft-error tolerance level similar to the S6P8N. Furthermore, it reduces the read access time (RAT) and write access time (WAT). Simulation results show that the proposed cells are self-recovery for all SNUs and most of DNUs. Compared with RHD12, QCCM12T, QUCCE12T, RHMD10T, SEA14T, RHM-12T, S4P8N, S8P4N, RH-14T, HRLP16T, CC18T, and RHM, the average power consumption of S6P8N is reduced by 48.78%, and the average WAT is reduced by 6.62%. While the average power consumption of S8P6N is reduced by 23.64%, and the average WAT and RAT by 9.07% and 36.84%, respectively. Index Terms: Double-node upsets (DNUs), high-speed, low power, self-recovery, static random access memory (SRAM).

List of the following materials will be included with the Downloaded Backup:One-Sided Schmitt-Trigger-Based 9T SRAM Cell for Near-Threshold Operation

Abstract:

This paper presents a one-sided Schmitt-trigger based 9T static random access memory cell with low energy consumption and high read stability, write ability, and hold stability yields in a bit-interleaving structure without write-back scheme. The proposed Schmitt-trigger-based 9T static random access memory cell obtains a high read stability yield by using a one-sided Schmitt-trigger inverter with a single bit-line structure. In addition, the write ability yield is improved by applying selective power gating and a Schmitt-trigger inverter write assist technique that controls the trip voltage of the Schmitt-trigger inverter. The proposed Schmitt-trigger-based 9T static random access memory cell has 0.79, 0.77, and 0.79 times the area, and consumes 0.31, 0.68, and 0.90 times the energy of Chang’s 10T, the Schmitt-trigger-based 10T, and MH’s 9T static random access memory cells, respectively, based on 22-nm Fin FET technology.

List of the following materials will be included with the Downloaded Backup:ReLOPE: Resistive RAM-Based Linear First-Order Partial Differential Equation Solver

Abstract:

Data movement between memory and processing units poses an energy barrier to Von-Neumann-based architectures. In-memory computing (IMC) eliminates this barrier. RRAM-based IMC has been explored for data-intensive applications, such as artificial neural networks and matrix-vector multiplications that are considered as “soft” tasks where performance is a more important factor than accuracy. In “hard” tasks such as partial differential equations (PDEs), accuracy is a determining factor. In this brief, we propose ReLOPE, a fully RRAM crossbar-based IMC to solve PDEs using the Runge–Kutta numerical method with 97% accuracy. ReLOPE expands the operating range of solution by exploiting shifters to shift input data and output data. ReLOPE range of operation and accuracy can be expanded by using fine-grained step sizes by programming other RRAMs on the BL. Compared to software-based PDE solvers, ReLOPE gains 31.4× energy reduction at only 3% accuracy loss.

List of the following materials will be included with the Downloaded Backup:Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability for Aerospace Applications

Abstract:

With the advancement of technology, the size of transistors and the distance between them are reducing rapidly. Therefore, the critical charge of sensitive nodes is reducing, making SRAM cells, used for aerospace applications, more vulnerable to soft-error. If a radiation particle strikes a sensitive node of the standard 6T SRAM cell, the stored data in the cell are flipped, causing a single-event upset (SEU). Therefore, in this paper, a Soft-Error-Aware Read-Stability-Enhanced Low Power 12T (SARP12T) SRAM cell is proposed to mitigate SEUs. To analyze the relative performance of SARP12T, it is compared with other recently published soft-error-aware SRAM cells, QUCCE12T, QUATRO12T, RHD12T, RHPD12T and RSP14T. All the sensitive nodes of SARP12T can regain their data even if the node values are flipped due to a radiation strike. Furthermore, SARP12T can recover from the effect of single event multi-node upsets (SEMNUs) induced at its storage node pair. Along with these advantages, the proposed cell exhibits the highest read stability, as the ‘0’-storing storage node, which is directly accessed by the bit line during read operation, can recover from any upset. Furthermore, SARP12T consumes the least hold power. SARP12T also exhibits higher write ability and shorter write delay than most of the comparison cells. All these improvements in the proposed cell are obtained by exhibiting only a slightly longer read delay and consuming slightly higher read and write energy.

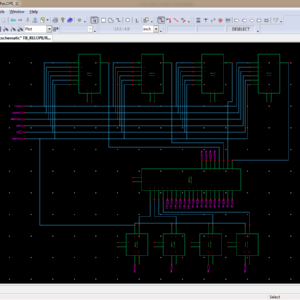

List of the following materials will be included with the Downloaded Backup:Soft-Error-Aware SRAM with Multinode Upset Tolerance for Aerospace Applications

Base Paper Abstract:

As technology scales down, the critical charge (QC) of vulnerable nodes decreases, making SRAM cells more susceptible to soft errors in the aerospace industry. This article proposes a Soft-Error-Aware 16T (S8P8N) SRAM cell for aerospace applications to address this issue. The properties of S8P8N are evaluated and compared with 6T, DICE, QUCCE12T, WEQUATRO, RHBD10T, RHBD12T, S4P8N, SEA14T, and SRRD12T. Simulation results indicate that all vulnerable nodes and key node pairs of the proposed cell can recover to their original states when affected by a soft error. Additionally, it can recover from key multinode upsets. The write speed of the proposed cell is found to be reduced by 20.3%, 50.1%, 74.1%, 63.7%, and 50.41% compared to 6T, DICE, QUCCE12T, WEQUATRO, and RHBD10T, respectively. The read speed of the proposed cell is found to be reduced by 56.6%, 52.2%, 62.5%, and 35.2% compared to 6T, SRRD12T, RHBD12T, and S4P8N, respectively. It also shows that the hold power of the proposed cell is found to be reduced by 14.1%, 13.8%, 17.7%, and 23.4% compared to DICE, WEQUATRO, RHBD10T, and RHBD12T. Furthermore, the read static noise margin (RSNM) of the proposed cell is found to be enhanced by 157%, 67%, and 32% compared to RHBD12T, SEA14T, and SRRD12T. All these improvements are achieved with a slight area penalty.

List of the following materials will be included with the Downloaded Backup:Provide Wordlwide Online Support

We can provide Online Support Wordlwide, with proper execution, explanation and additionally provide explanation video file for execution and explanations.

24/7 Support Center

NXFEE, will Provide on 24x7 Online Support, You can call or text at +91 9789443203, or email us nxfee.innovation@gmail.com

Terms & Conditions:

Customer are advice to watch the project video file output, and before the payment to test the requirement, correction will be applicable.

After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

Online support will not be given more than 3 times.

On first time explanation we can provide completely with video file support, other 2 we can provide doubt clarifications only.

If any Issue on Software license / System Error we can support and rectify that within end of day.

Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

After payment, to must send the payment receipt to our email id.

Powered by NXFEE INNOVATION, Pondicherry.

Call us today at : +91 9789443203 or Email us at nxfee.innovation@gmail.com

NXFEE Development & Services

Copyright © 2026 Nxfee Innovation.