Proposed Title :

A 45nm and 65 nm CMOS Implementation Class C/D VCO for Ultralow-power Appliations

Improvement of this Project:

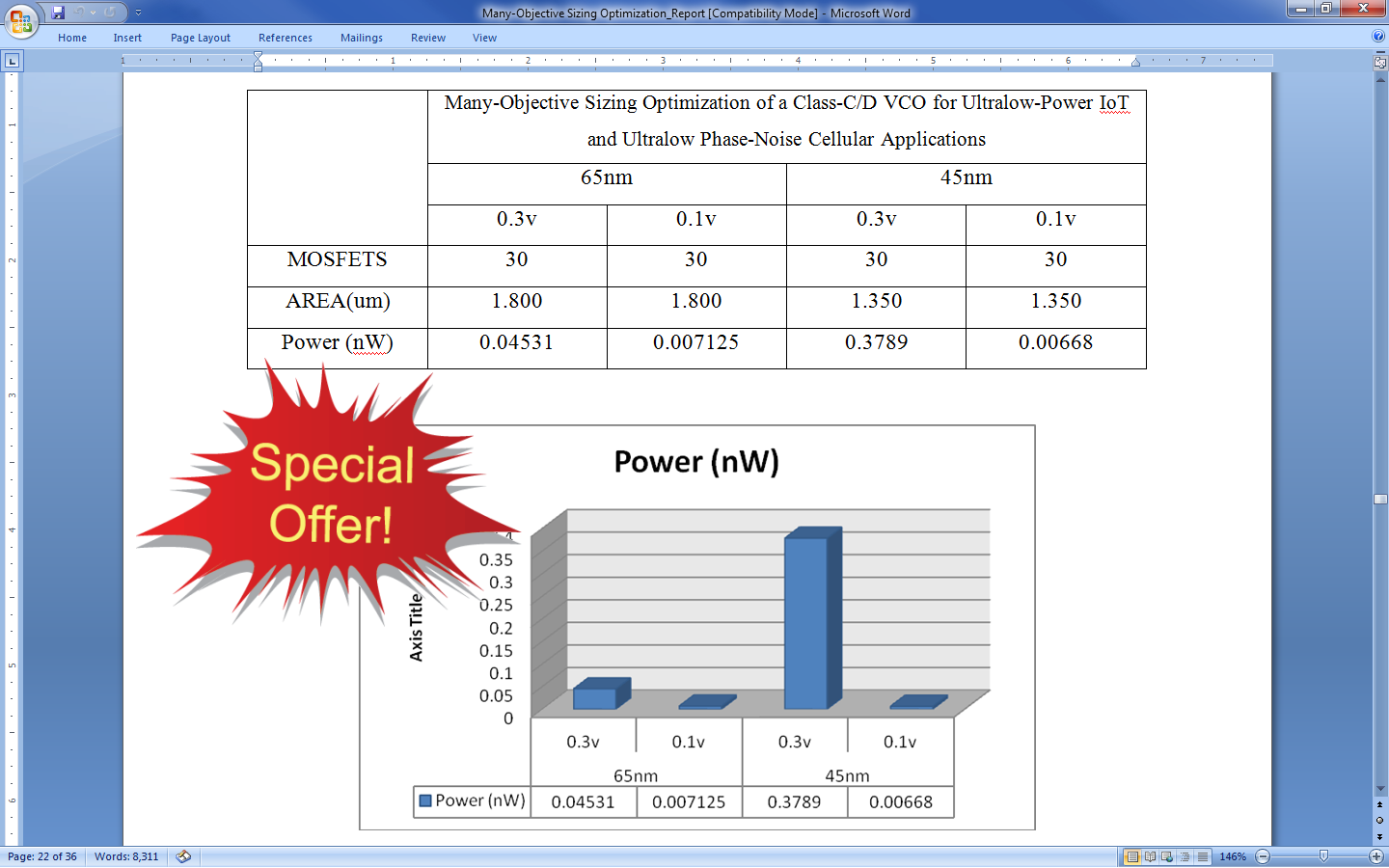

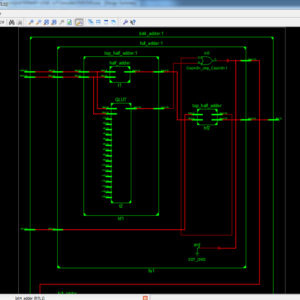

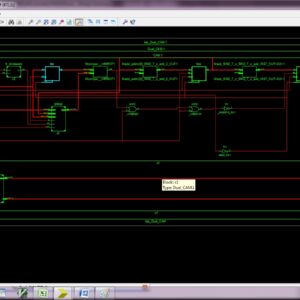

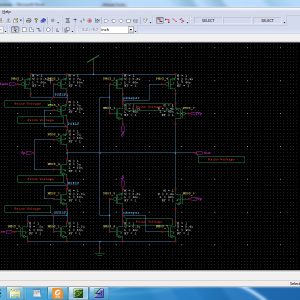

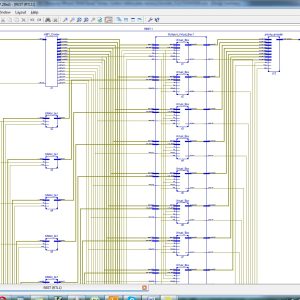

To develop this Class C/D Voltage Control oscillators at 45nm CMOS Technology, at 0.1V with compared and proved the performance of Area, Delay and Power to existing 65nm CMOS Technology.

Software implementation:

- TANNER EDA

Proposed System:

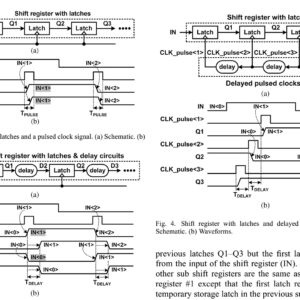

In this paper performance boundaries and corresponding tradeoffs of a complex dual-mode class-C/D voltage controlled oscillator (VCO) it will play a major key role in modern radio frequency of integrated circuit with multi standard transceivers and receivers. These VCO embedded in the state of the art multi standard transceivers must comply with extremely high performance and ultra low power requirements for modern cellular and internet of things applications, and it’s should maintain low power consumptions while the phase noise performance can be quite relaxed. Here, the paper presents the dual mode design and optimization of complex dual mode class C/D VCO will integrated with 5 MHZ ~ 10 MHz frequency range with 0.1V to 0.3V with perform in the CMOS technology of 45nm and 64nm. Finally this work will designed in Tanner EDA tool and proved the comparisons of low power consumptions in difference of 45nm and 65nm CMOS technology.

” Thanks for Visit this project Pages – Buy It Soon “

Many-Objective Sizing Optimization of a Class-C/D VCO for Ultralow-Power IoT and Ultralow Phase-Noise Cellular Applications

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link