Proposed Title :

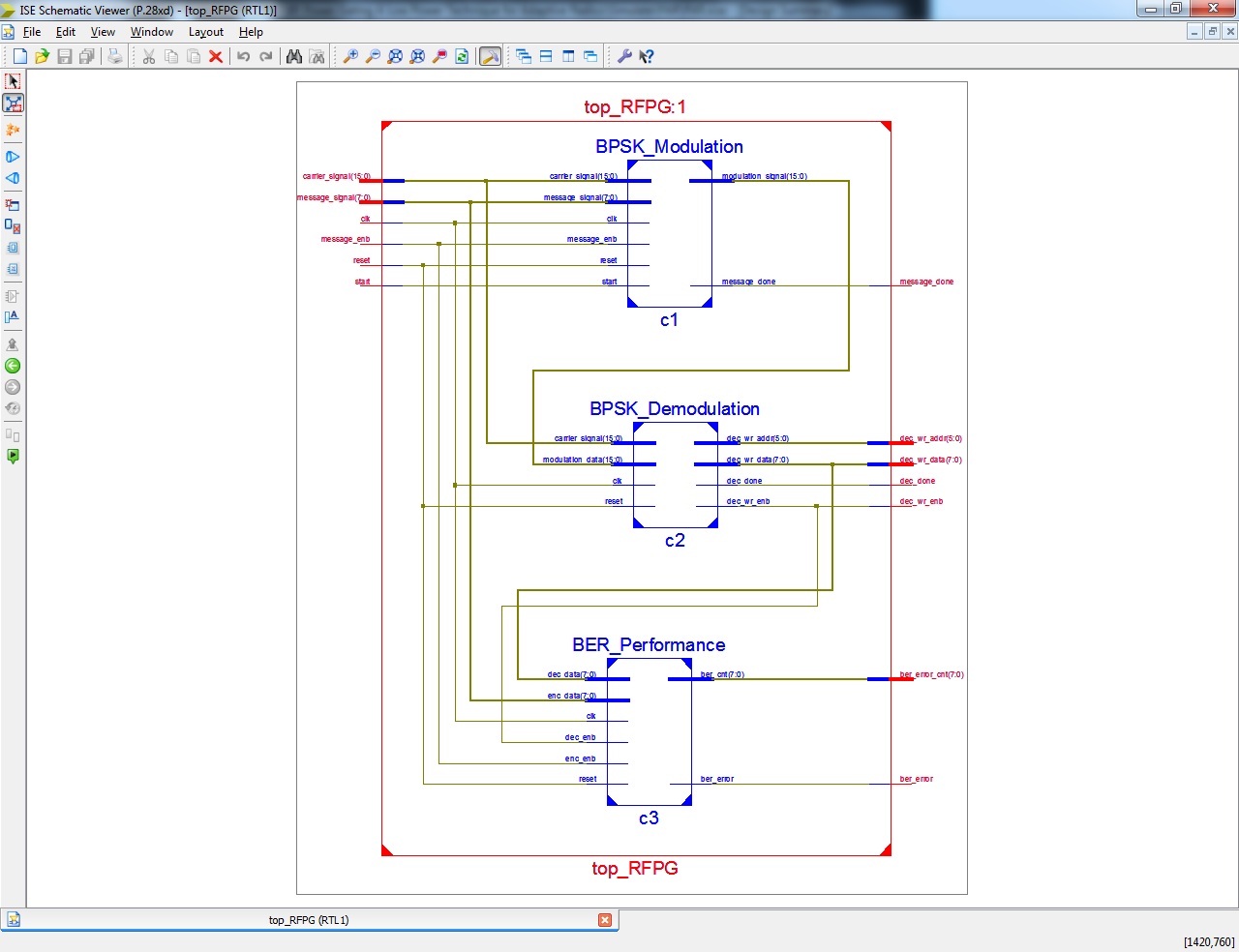

FPGA Implementation of RF Power Gating with Low Power Technique of Adaptive Radios using BPSK Modulation

Improvement of this Project:

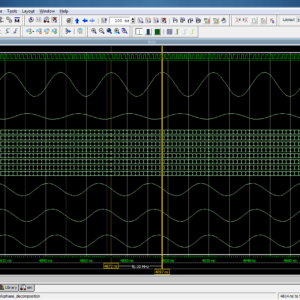

- Modified the MSK (Minimum Shift Keying) to BPSK ( Binary Shift Keying)

- Less Bandwidth

- Power Consumption is less

- High Speed data Transfer with Multi-Bit Differential Signal

- Less BER Error rate

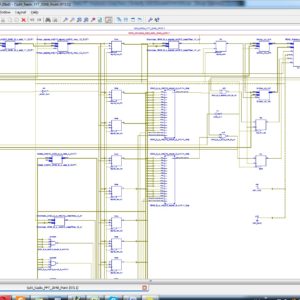

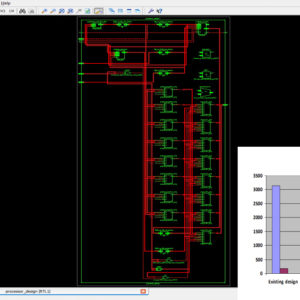

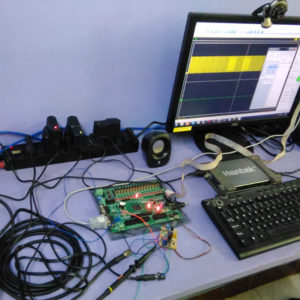

Software implementation:

- Modelsim

- Xilinx 14.2

Proposed System:

The technique presented throughout this paper is part of adaptive radios field and aims at scaling the RX performances with the power consumption without changing the RX architecture. This technique, called RF Power gating ( RFPG), consists in extending the sleep mode scheme from the frame-to-frame scale to the symbol time scale. In other words, each fast enough RF front-end component will be modified to BPSK modulation, will be send the data through phase shifting to increases the BER performance, and also reduced the power consumption compared to the existing system. While the analog blocks are only required to settle fast enough to be RFPG-compliant, the RF front-end architecture is to allow switching between the full performances reception and the low power mode. As a results, the RFPG-related processing is done with digital blocks, which also allows benefiting from advances in the next generation technology.

This paper expresses and underlined the tradeoff between the BER Performances degradation due to not observing the BPSK modulation signal during the whole symbol time and the power saving obtained. The study presented gives to the designers, interested in using this adaptive solution with their full performances RXs, with modified receiver with the help of BPSK demodulation.

” Thanks for Visit this project Pages – Buy It Soon “

RF Power Gating A Low Power Technique for Adaptive Radios

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link