Proposed Title :

FPGA Implementation of Light Weight Ring Generator based True Random Number Generator using Metastability with Clock Managers

Improvement of this project :

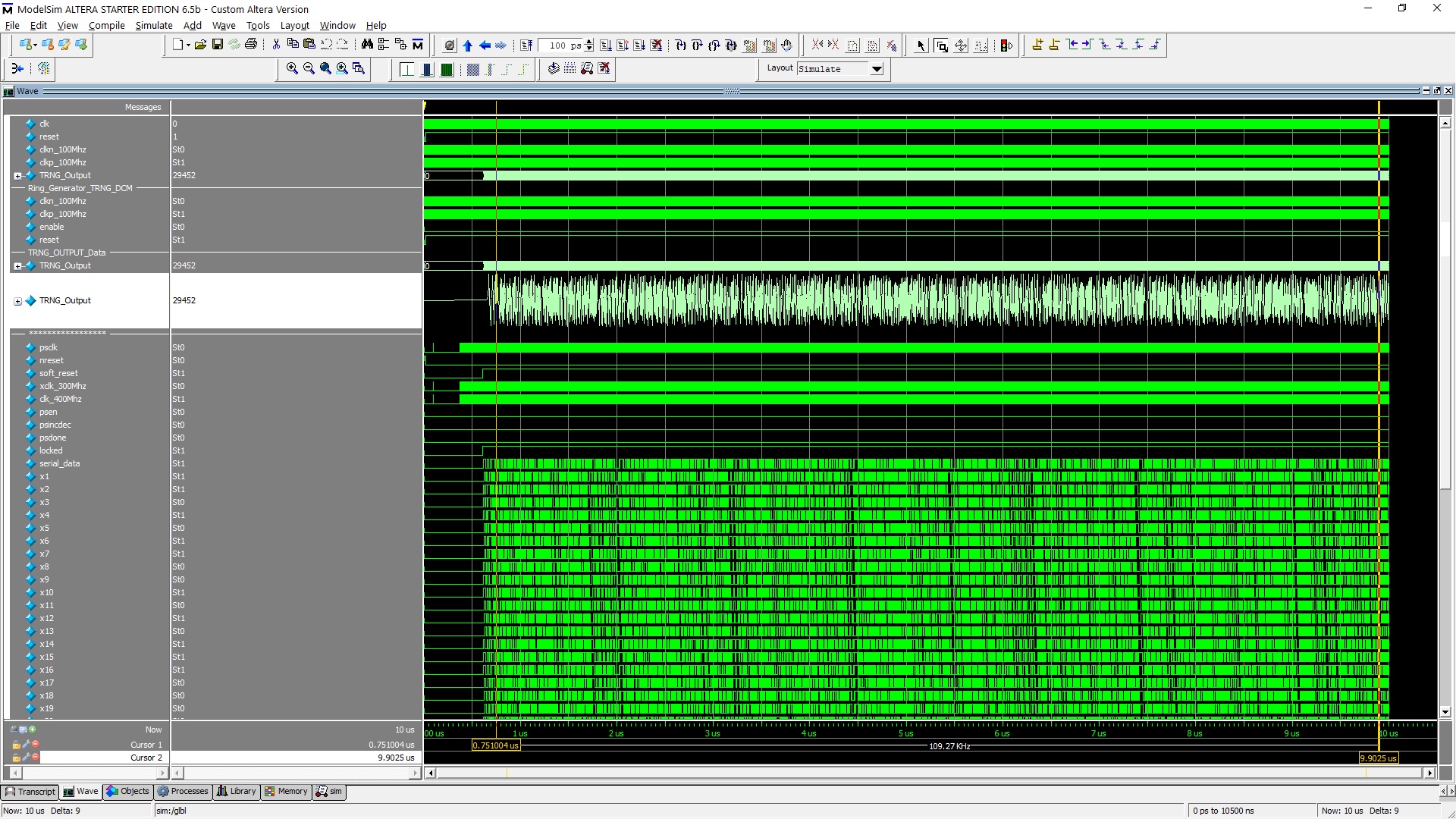

To design the Ring Generator based True Random Number Generator using Digital Clock Managers (DCM).

To reduce the Metastability, jitter and randomness error with the help of Digital Clock Managers

The proposed TRNG also tested with BIST Controller and proved the test sequence

Software Implementation:

- Modelsim

- Xilinx

Proposed System:

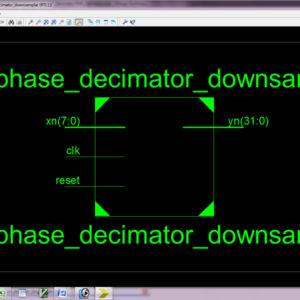

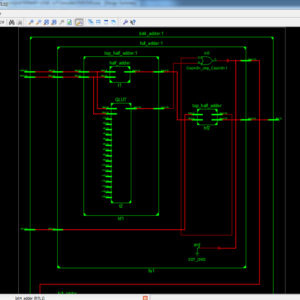

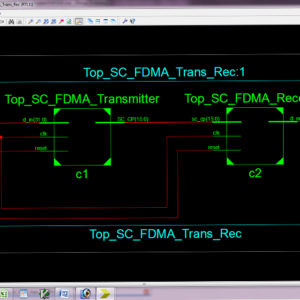

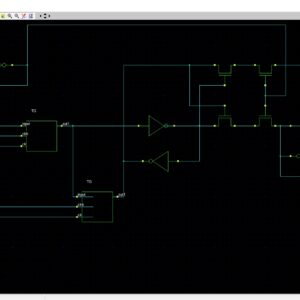

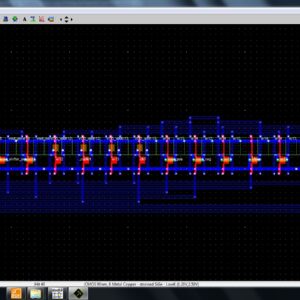

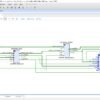

There are numerous systems proposed to secure integrated circuits (ICs) from illegal access and usage, or to at least lessen security threats. They establish the groundwork for hardware trust roots whose critical security primitives are generators of truly random numbers. Such generators are used in particular to generate one-time challenges and to assist the IC authentication procedures used to fight potential risks such as untrusted people accessing ICs. However, IC suppliers have raised various concerns about the complexity of these solutions, including the influence on design flow and testability. TRNGs, or true random number generators, are crucial components of a wide range of vital security applications. Despite the fact that digital-based solutions utilize randomness sources that are commonly found in the analog domain, digital-based solutions are critical, especially when they must be implemented on Field Programmable Gate Array (FPGA)-based digital systems. This study describes a novel approach for simplifying the construction of a TRNG using FPGA devices. It makes advantage of the runtime capabilities of the hardware primitives offered by the Digital Clock Manager (DCM) to adjust the random number generation with clock signals and to minimize Metastability, Jitter, and Randomness Error. It is based on the design of a generic ring generator, which is an area and time optimized version of a linear feedback shift register driven by a multiple-output ring oscillator. This work was created in Verilog HDL with an 8-bit data width and generated on a Xilinx Vertex-5 FPGA. All of the properties were examined in terms of area, latency, and power usage.

” Thanks for Visit this project Pages – Buy It Soon “

A Lightweight True Random Number Generator for Root of Trust Applications

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.