Proposed Title :

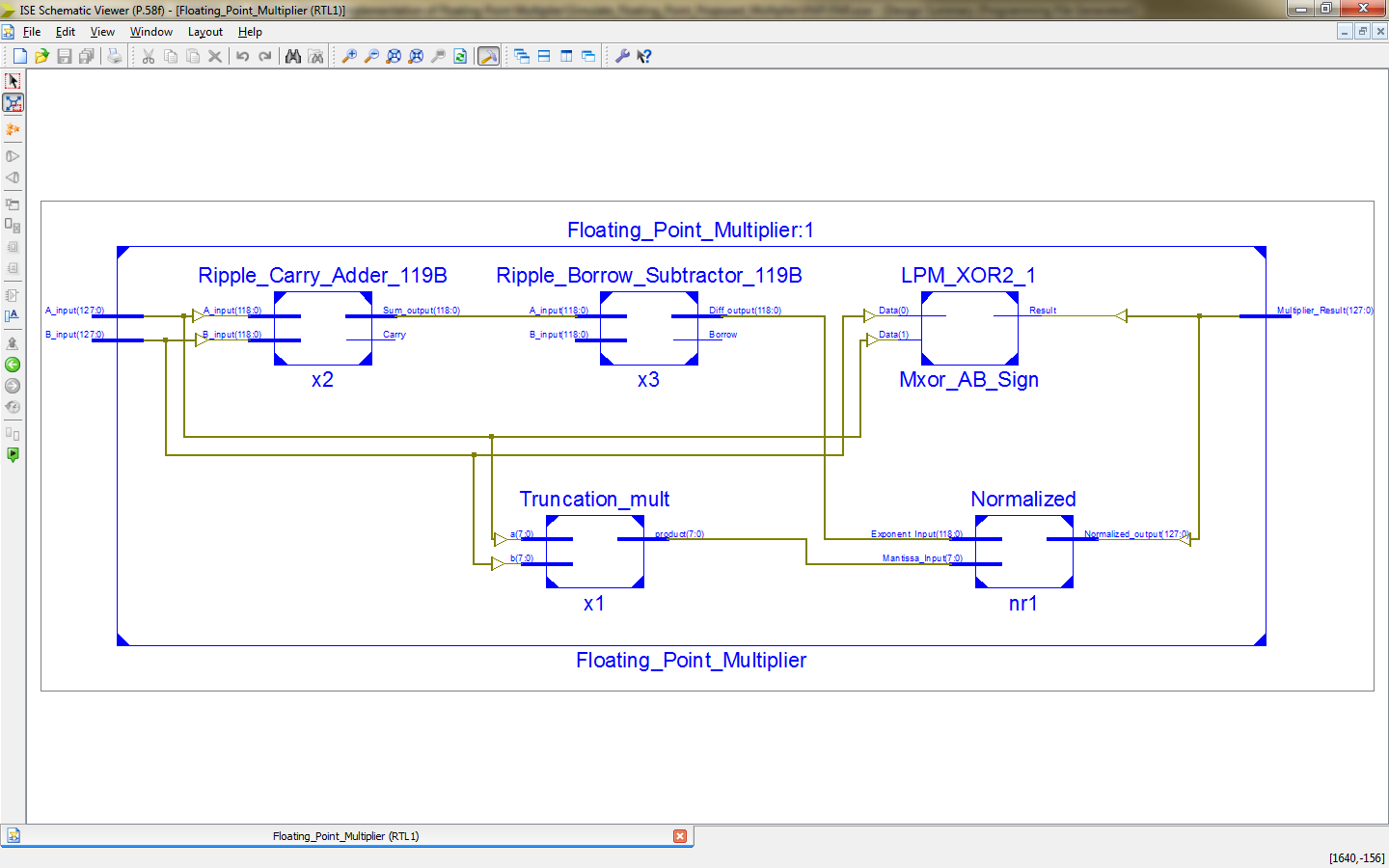

FPGA Implementation of 128-Bit Floating Point Multiplier with using Truncated Rounding Method

Improvement of this Project:

-

To re-modified the carry save multiplier to Truncated Multiplier and reduce number of full adder and output bit size in multiplier logic.

-

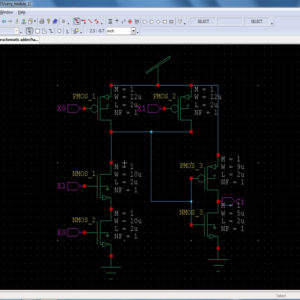

To integrate XOR MUX full adder instead of Conventional full adder in all the adding circuit and reduce the number of logic gates, delay and power.

Software implementation:

- Xilinx

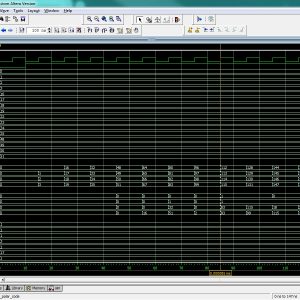

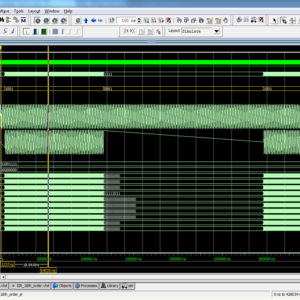

- Modelsim

Proposed System:

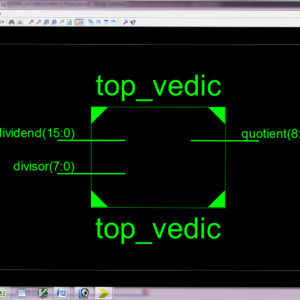

In this paper present, an efficient implementation of double extend approximation method of floating point multiplier target for Xilinx Vertex 5 FPGA using Verilog HDL. The floating point implementation will cover up with 119-bit exponent, 8 bit mantissa, and 1 sign bit. This proposed architecture implement with Approximate Truncated Multiplier to reduce the n-size output in multiplier operation instead of carry save multiplier and replace the number of full adder and full Subtractor using XOR-MUX logic to reduce the number of logic gates in floating point multiplier architecture. Finally, done this architecture with normalized rounding method and to reduce area, delay and power. The error difference will analyzed using Modelsim Software, and analyses optimized logic size’s, delay and power in proposed vs existing multiplier.

” Thanks for Visit this project Pages – Buy It Soon “

An Efficient Implementation of Floating Point Multiplier