Proposed Title :

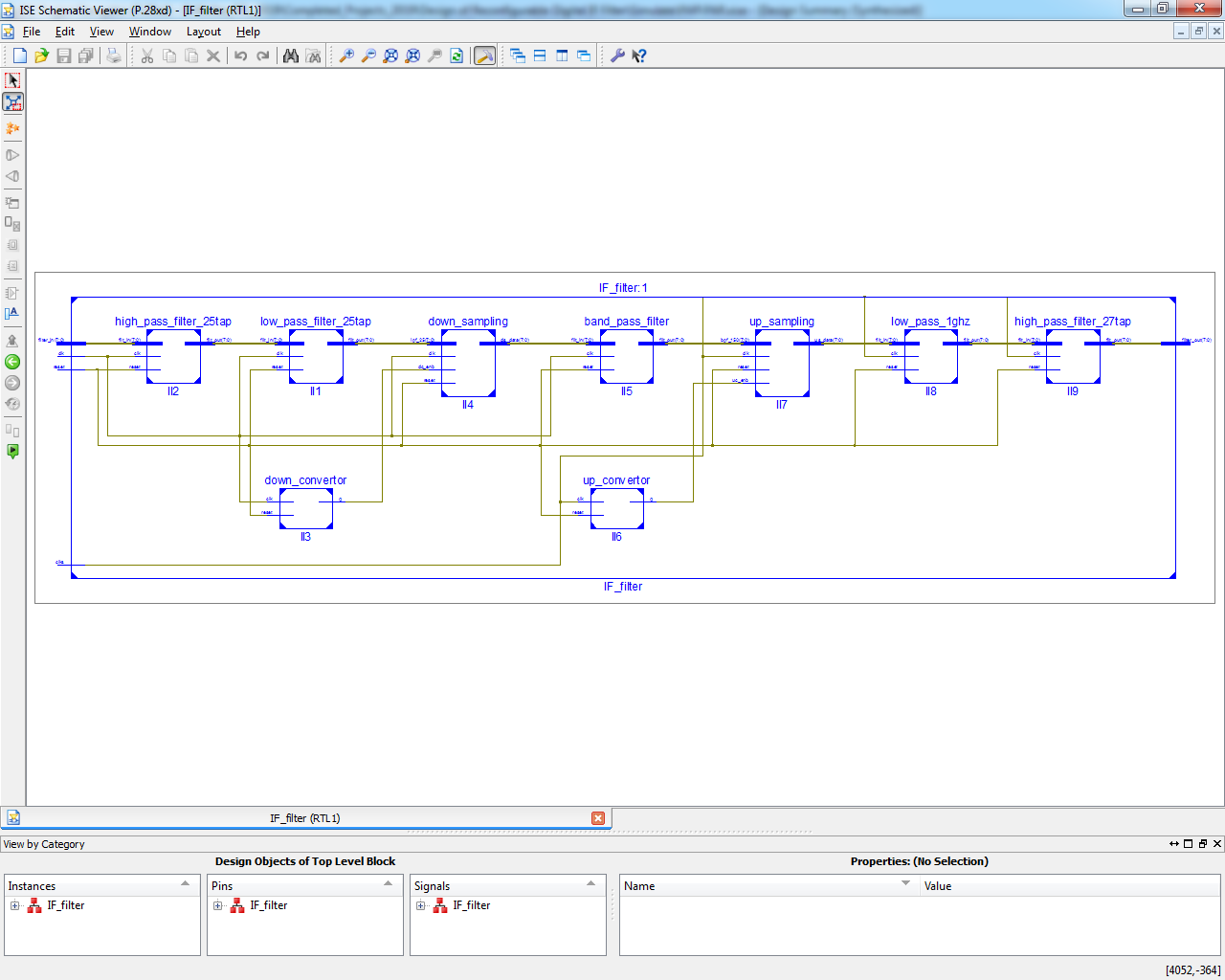

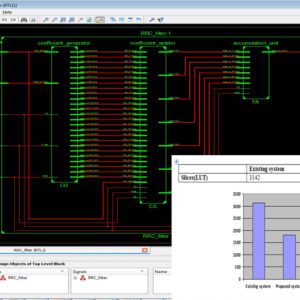

Design of Low Complexity and Efficient Reconfigurable Digital IF Filter using Multi Stage Filter Bank.

Improvement of this Project:

To Design a reconfigurable Digital IF Filter with variable center frequency and bandwidth.

The centre frequency can be varied from the 500MHZ to 1GHZ and filter bandwidth can be selective to one of 10MHZ, 15MHZ and 20MHZ frequency level.

Design all the Multipliers in Truncated method

Software implementation:

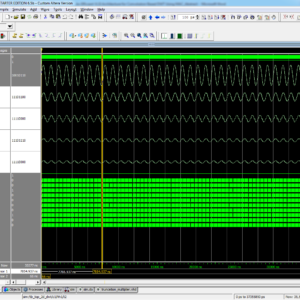

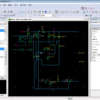

- Modelsim

- Xilinx

Proposed System:

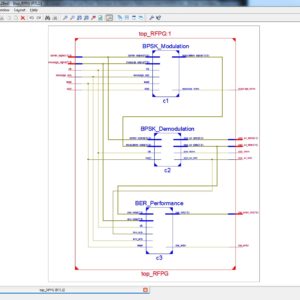

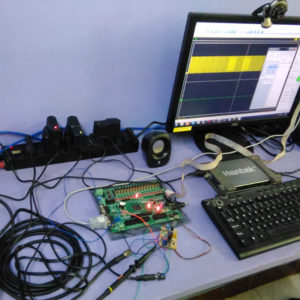

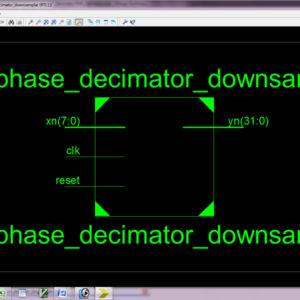

Due to limited frequency resources, new services are being applied to the existing frequencies, and service providers are allocating some of the existing frequencies for newly enhanced mobile communications. Because of this frequency environment, repeater and base station systems for mobile communications are becoming more complicated, and frequency interference caused by multiple bands and services is getting worse. The IF (Intermediate Frequency) Filters with high selectivity is used to reduce the interference between the different frequency range. Therefore, the heterodyne receivers uses the IF filter. In mobile communication the repeaters and the base station cannot actively cope because, it has fixed frequency range. Therefore, this paper proposes the new design concept of low complexity and efficient reconfigurable digital IF filters using multi stage filter bank. The multi stage filter bank of the proposed digital IF filters lowering the sample rate in order to reduce the hardware complexity. The existing system of digital IF filters uses the concept of SAW(surface acoustic wave) IF filter, it has high frequency stability and selectivity but, it does not have variable centre frequency. The SAW IF filters has the fixed frequency level only. Therefore the proposed system of digital IF filters uses the concept of multi stage filter bank in order to reduces the hardware complexity and better performance. The proposed digital IF filters uses the different centre frequency from the range of 500MHZ to 1GHZ and filter bandwidth can be selective to one of 10MHZ, 15MHZ and 20MHZ frequency level. The proposed digital IF filter reduces the complexity of adders and multipliers. Finally, The Digital IF filter using multi stage filter bank in VHDL and synthesized in the XILINX FPGA-S6LX9 and shown the comparison in terms of area, power and delay reports.

” Thanks for Visit this project Pages – Buy It Soon “

Design of Reconfigurable Digital IF Filter with Low Complexity

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link