Proposed Title :

Modified High Definition SPWM Generation on FPGAs with Harmonic

Mitigation for Voltage Source Inverter Applications

Improvement of this Project:

-

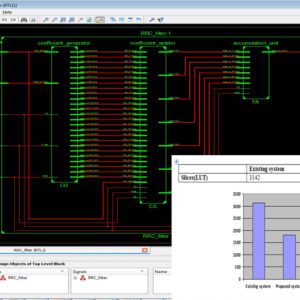

To design and modified the Hardware architecture of High Definition SPWM Generation With Harmonic Mitigation System due to performance utilization and hence proved with area, delay and power comparisons.

· To design the sampling frequency at 4 MHz and switching frequency at 20 KHz range.

· To design the proposed hardware architecture at Vertex 7 FPGA, regarding to improve the performance range of high speed utilization.

Software implementation:

- Modelsim

- Xilinx

Proposed System:

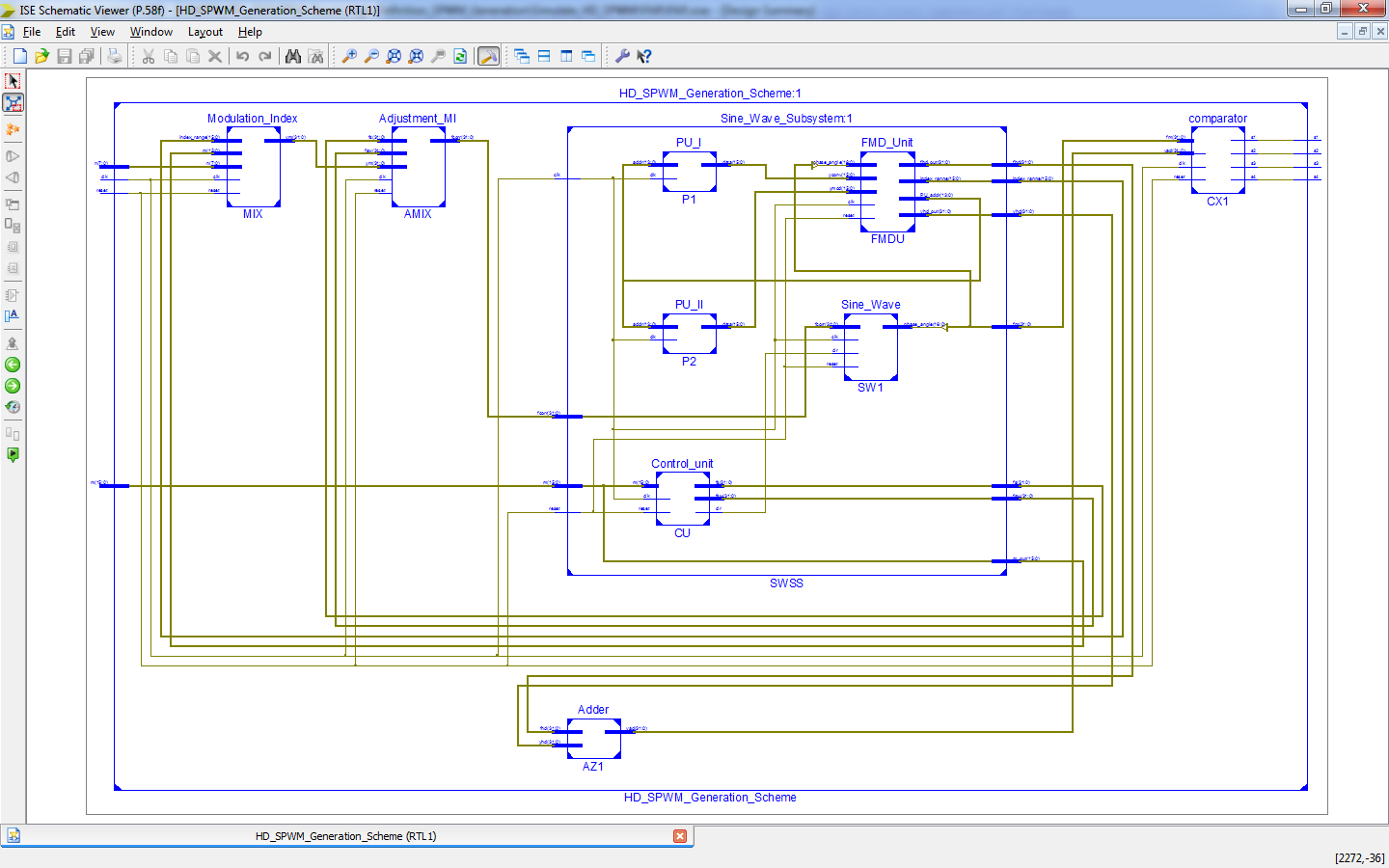

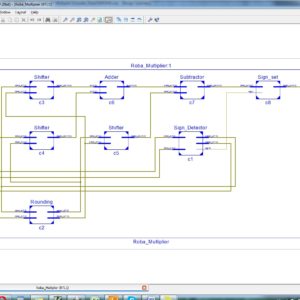

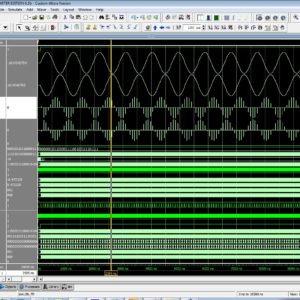

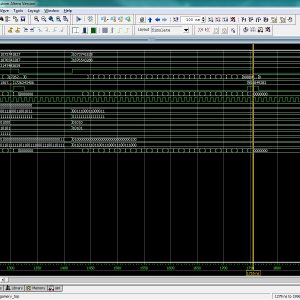

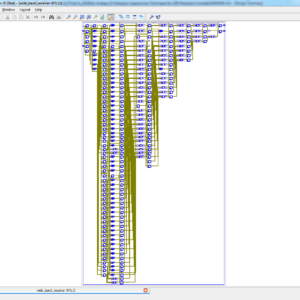

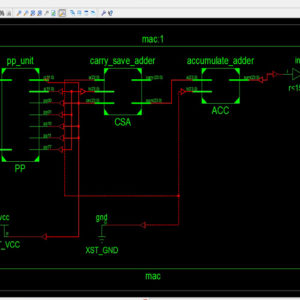

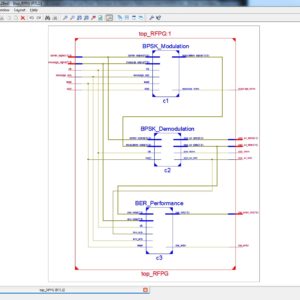

Switching using high resolution sinusoidal pulse width modulation (SPWM) is advantageous in order to produce limited capability and fine sinusoidal output of dc-ac converters. This paper proposes a unique FPGA based high definition SPWM ( HD-SPWM) architecture for integrating a lower frequency PWM train to a high frequency SPWM train in order to minimize inverter output with harmonics while attaining high resolution output. An optimized FPGA based two stage finite state machine (FSM) architecture is designed, where the initial stage decide pulse widths of a lower frequency PWM train based on the premeditate pulse width of the high frequency SPWM train, and the final stage integrates lower frequency PWM pulse width the high frequency SPWM pulse widths to generate updated high frequency SPWM pulse width, i.e HD-SPWM. Furthermore, a pre-formulation mathematical model for calculating duty cycle count value of pulse trains is constructed to allow the continuous modification of the HD modulation SPWM’s index (MI). The suggested generation has the advantages of harmonic mitigation, continuous fine adjustment of MI, quick processing time, and the demand of a small portion of a medium sized FPGA resulting in a favorable tradeoff between bigger designs and greater performance. Finally the proposed approach to design and modified the Hardware architecture of High Definition SPWM Generation With Harmonic Mitigation System due to performance utilization and hence proved with area, delay and power comparisons. To design the sampling frequency at 4 MHz and switching frequency at 20 KHz range. To design the proposed hardware architecture at Vertex 7 FPGA, regarding to improve the performance range of high speed utilization.

” Thanks for Visit this project Pages – Buy It Soon “

FPGA Based High Definition SPWM Generation With Harmonic Mitigation Property for Voltage Source Inverter Applications

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.