Proposed Title :

FPGA Implementation of High Throughput Retinex Algorithm for Real Time Image and Video Enhancement

Improvement of this Project:

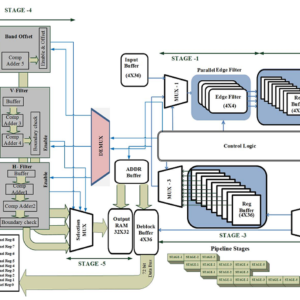

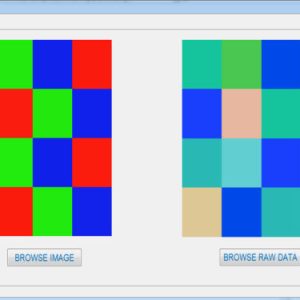

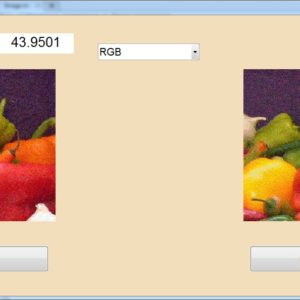

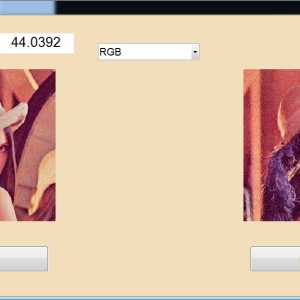

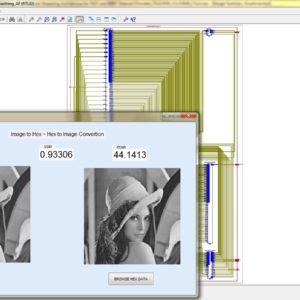

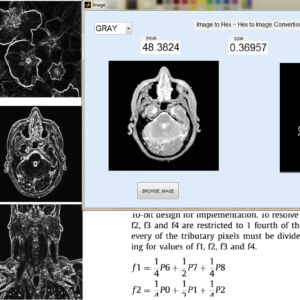

To implement Gaussian Smoothing Filter with using Image line Buffer to Split and reconstruct 3×3 image convolution at the 720×576 image resolution.

To implement a Retinex Algorithm at 720×576 image resolution, and compared with Li [27] and Marsi [29].

To implement Image Enhancement method approach of Contrast addition and subtraction in the final stage of Retinex algorithm.

Software implementation:

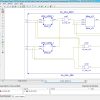

- Modelsim

- Xilinx

Proposed System:

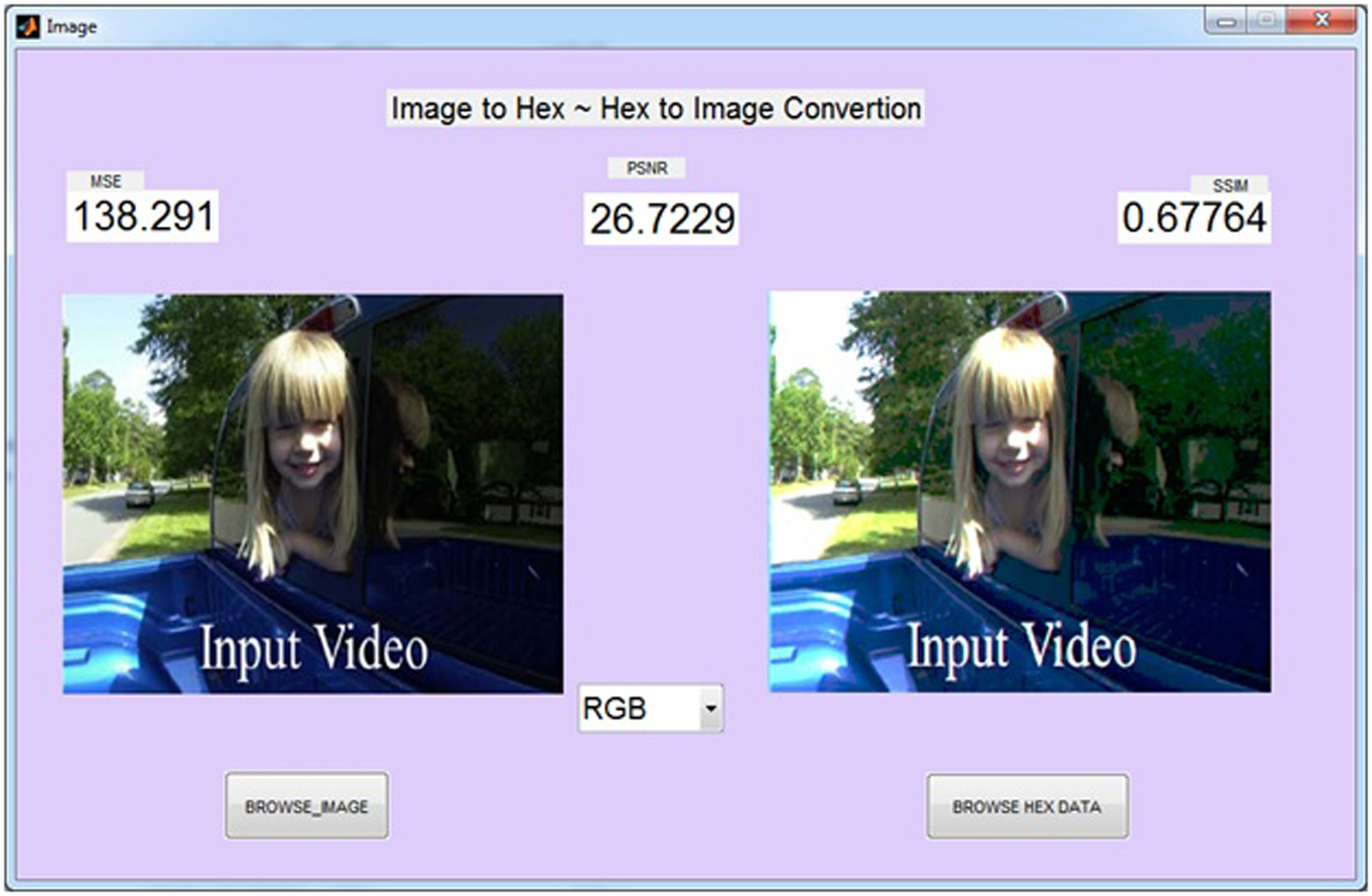

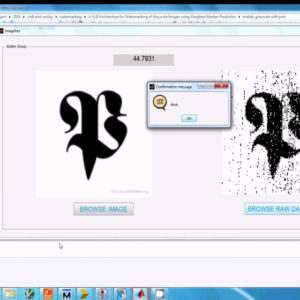

As a result of low illumination circumstances, the image sensor is often degraded in specific environment of video applications such as medical imaging, space exploration, and underwater research, among other things. As a result, it is important to brighten the portion of the image that is too dark to detect features while keeping the remainder of the image at its original brightness. With the retinex algorithm, video naturalness may be restored more effectively than ever before, and the method performs particularly well in the augmentation of a dark region. The sophisticated structure, such as the Gaussian filter and exponentiation operations, necessitates a high level of computing complexity, which makes it difficult to execute in real time because of the high level of computational complexity required. Presented in this proposed approach is a low-cost and high-throughput design for the retinex video enhancement method, using a field-programmable gate array (FPGA), the design is developed, and it can produce images at a rate of 60 frames per second for a 720 x 576 resolution with very low latency. The proposed FPGA design reduces the amount of hardware resources required while maintaining the quality and performance. This is accomplished by employing a small line buffer rather than a frame buffer, by utilizing the concept of approximate computing for the complex Gaussian filter, and by developing a novel and nontrivial exponentiation operation. This work developed on Xilinx Vertex 5 FPGA and compared all the parameters in terms of area, delay and power.

” Thanks for Visit this project Pages – Buy It Soon “

A Low Cost and High Throughtput FPGA Implementation of the Retinex Algorithm for Real Time Video Enhancement

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.