Proposed Title :

FPGA Implementation of Gaussian noise reduction using Approximate Multiplier with Altered Partial Products

Proposed System:

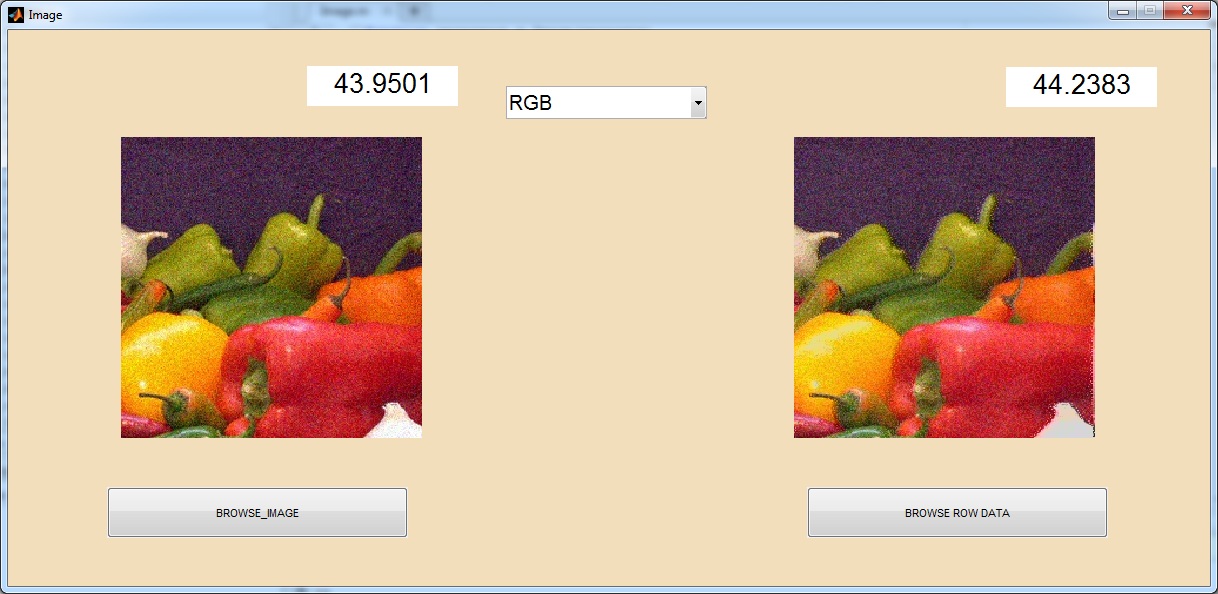

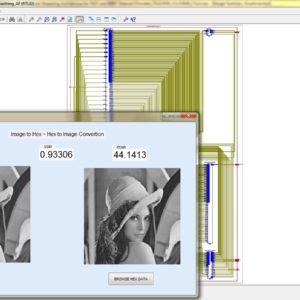

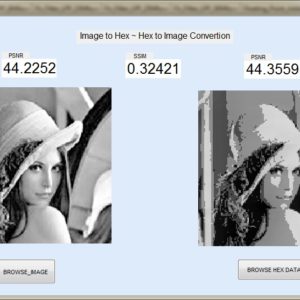

- The existing architecture of luminance (y) Gaussian noise reduction using Approximate multiplier with altered partial products, to modified with luminance (y) and chrominance (cb, cr) Gaussian noise reduction using Approximate multiplier with altered partial products.

Software implementation:

- Modelsim

- Xilinx

Proposed System:

The proposed hardware multiplier reduced the complexity and also truncated widely employed in fixed width multiplier design. Here the proposed multiplier approximate technique is fully focus on accumulation of partial products, which is crucial in terms of power consumption. The proposed multiplier saves few adder circuits in partial products, and this proposed multiplier is evaluated with an image processing application. In existing thing, to using this multiplier to design image processing evaluation on only luminance based application, but here the proposed work is modified with luminance and chrominance based application, this design to implemented in VHDL, and synthesized in Xilinx S6LX9 FPGA and shown the power, area and delay reports.

” Thanks for Visit this project Pages – Buy It Soon “

Design of Power and Area Efficient Approximate Multipliers

“Buy VLSI Projects On On-Line”

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link