Proposed Title :

FPGA Implementation of Energy Efficient ECG Signal Processing based on Approximate Pruned Haar Discrete Wavelet Transform

Improvement of this project :

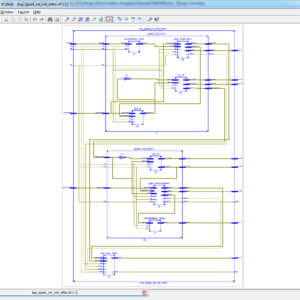

To design a Approximate Haar Wavelet Transform of Hardware architecture at three level of design ( Original HDWT, Approximate HDWT, Approximate Pruned HDWT ) using Conventional Full adder and XOR-MUX Full adder to reduced the number of logic size and power consumptions.

Software Implementation:

- Modelsim

- Xilinx

Proposed System:

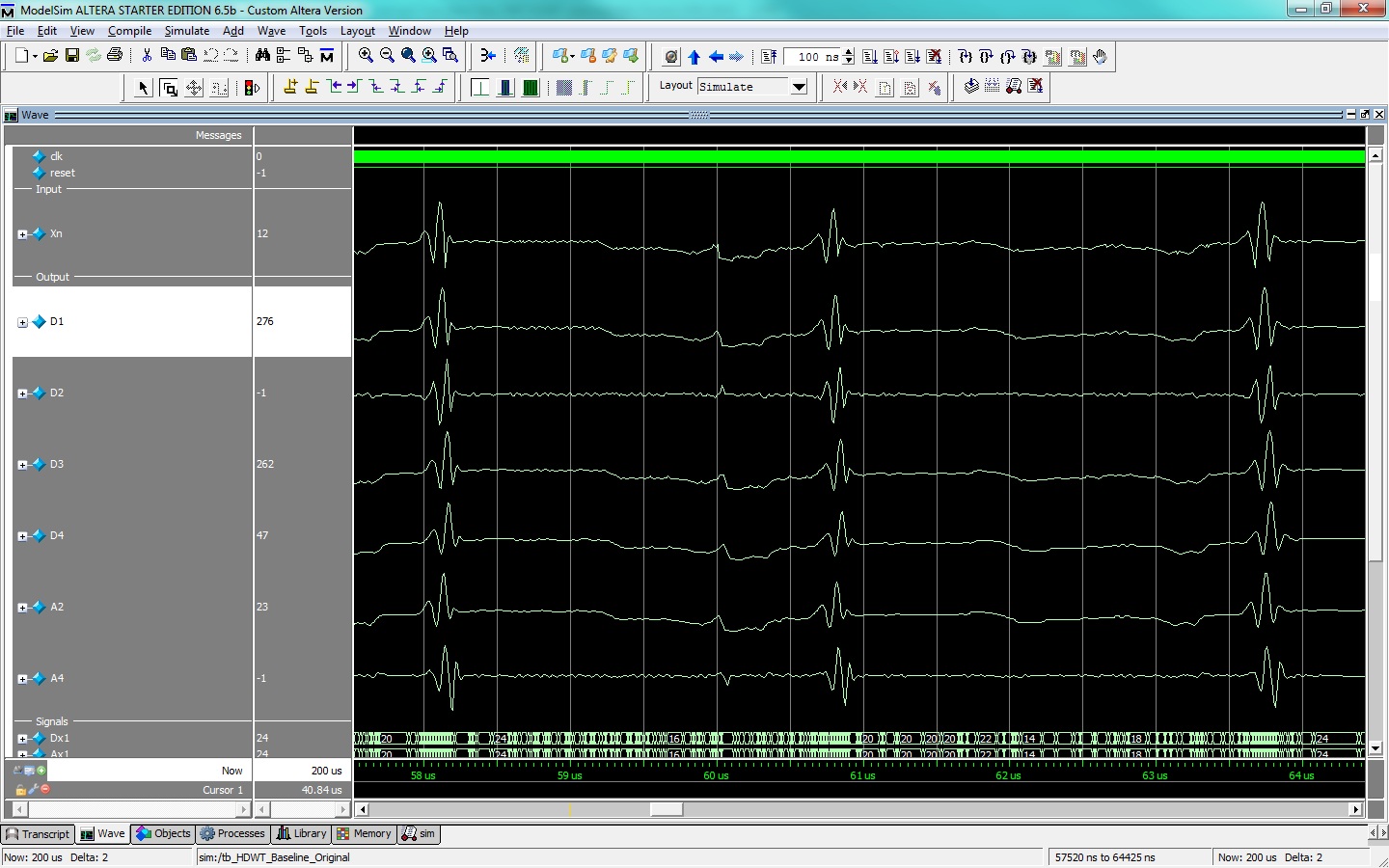

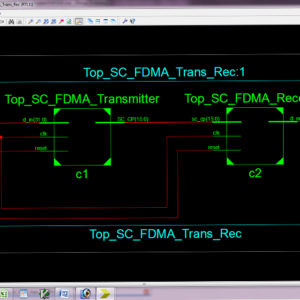

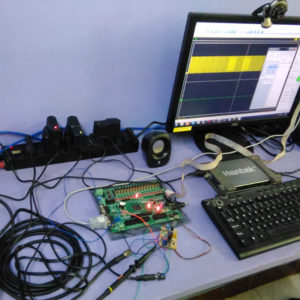

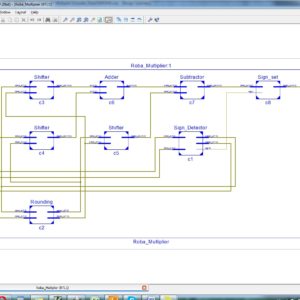

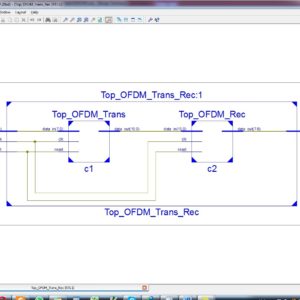

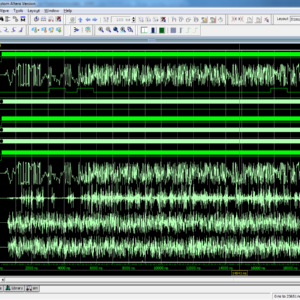

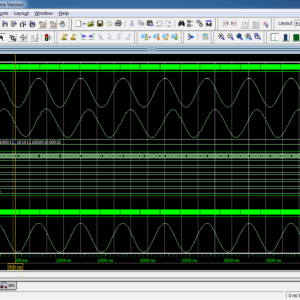

The methodology of approximation computing emerged as an ideal approach that allowed for the transfer of accuracy and energy efficiency. Error-tolerant programmes, which include signal processing and multimedia processing, are able to process the information with an accuracy that is lower than the norm while still satisfying a high and appropriate service quality at the application level. The important phase that comes just before the processing and analysis of an electrocardiogram (ECG) data is the automated recognition of R-peaks within the ECG signal. The Haar discrete wavelet transform (HDWT) is a low-complexity pre-processing filter that is appropriate for detecting ECG R-peaks in embedded systems such as wearable devices, which are subject to very stringent energy constraints. In this study, an approximate HDWT hardware architecture for ECG processing is presented with MIT-BIH Database. The energy efficiency of this design is quite good. Only 7 improvements are necessary for our top suggestion, which involves doing pruning inside the basic concept of the HDWT hardware design. The use of a truncation technique to improve energy efficiency is also investigated in this article by observing the development of the signal-to-noise ratio and the ultimate impact in the ECG peak-detection application. The proposed approach of this work gather about the effectiveness of the technique based on HDWT approximation hardware design approach using XOR MUX Full adder design instead of Conventional Full Adder design, and also design with higher levels of truncation than the normal HDWT. When we combined our HDWT matrix approximation proposal with the pruning and the highest acceptable level of truncation, our results showed a reduction in energy consumption that was approximately nine times greater than the previous level. Finally this work developed in Verilog HDL, and Synthesized on Xilinx Vertex-5 FPGA and compared all the parameters in terms of area, delay and power.

” Thanks for Visit this project Pages – Buy It Soon “

Approximate Pruned and Truncated Haar Discrete Wavelet Transform VLSI Hardware for Energy-Efficient ECG Signal Processing

Terms & Conditions:

- Customer are advice to watch the project video file output, before the payment to test the requirement, correction will be applicable.

- After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

- After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

- Online support will not be given more than 3 times.

- On first time explanations we can provide completely with video file support, other 2 we can provide doubt clarifications only.

- If any Issue on Software license / System Error we can support and rectify that within end of the day.

- Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

- After payment, to must send the payment receipt to our email id.

- Powered by NXFEE INNOVATION, Pondicherry.

Payment Method :

- Pay Add to Cart Method on this Page

- Deposit Cash/Cheque on our a/c.

- Pay Google Pay/Phone Pay : +91 9789443203

- Send Cheque through courier

- Visit our office directly

- Pay using Paypal : Click here to get NXFEE-PayPal link

Bank Accounts

HDFC BANK ACCOUNT:

- NXFEE INNOVATION,

HDFC BANK, MAIN BRANCH, PONDICHERRY-605004.

INDIA,

ACC NO. 50200013195971,

IFSC CODE: HDFC0000407.