Power Efficient Tiny Yolo CNN Using Reduced Hardware Resources Based on Booth Multiplier and WALLACE Tree Adders

Probability-Driven Evaluation of Lower-Part Approximation Adders

Radiation-Hardened 0.3–0.9-V Voltage-Scalable 14T SRAM and Peripheral Circuit in 28-nm Technology for Space Applications

Radiation-Hardened 14T SRAM Bit cell With Speed and Power Optimized for Space Application

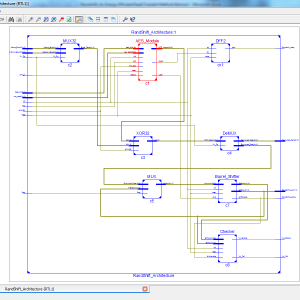

RandShift: An Energy-Efficient Fault Tolerant Method in Secure Nonvolatile Main Memory

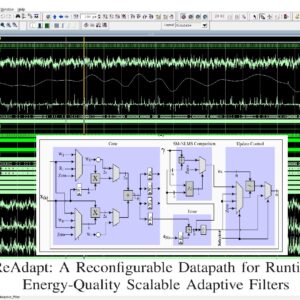

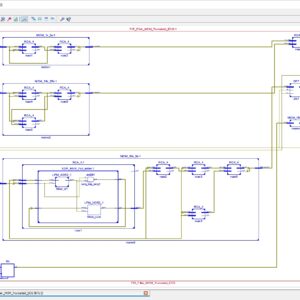

ReAdapt: A Reconfigurable Datapath for Runtime Energy-Quality Scalable Adaptive Filters

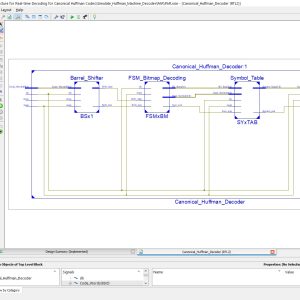

Reconfigurable Architecture for Real-time Decoding of Canonical Huffman Codes

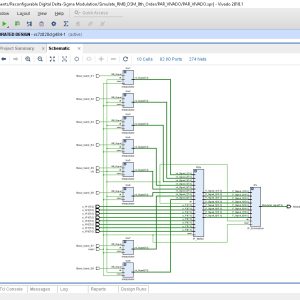

Reconfigurable Digital Delta-Sigma Modulation Transmitter Architecture for Concurrent Multi-Band Transmission

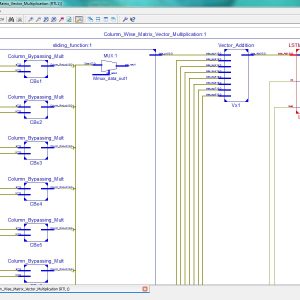

Recurrent Neural Networks With Column-Wise Matrix–Vector Multiplication on FPGAs

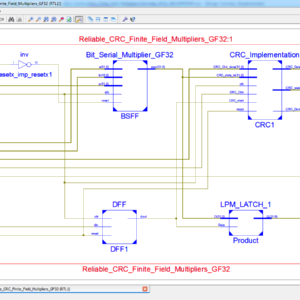

Reliable CRC Based Error Detection Constructions for Finite Field Multipliers With Applications in Cryptography

ReLOPE: Resistive RAM-Based Linear First-Order Partial Differential Equation Solver

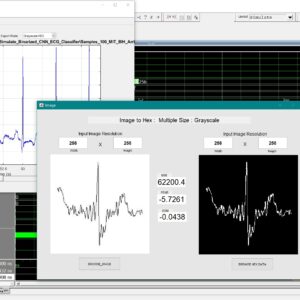

Resource and Energy Efficient Implementation of ECG Classifier using Binarized CNN for Edge AI Devices

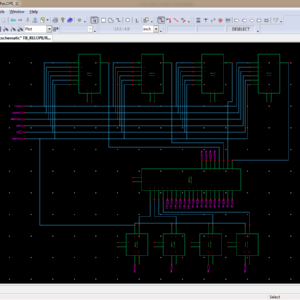

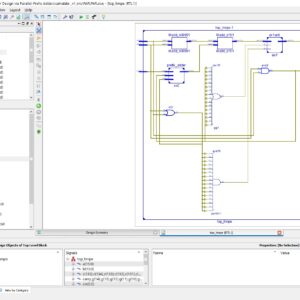

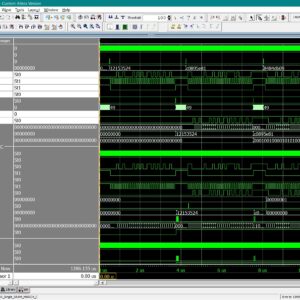

Reverse Converter Design via Parallel-Prefix Adders: Novel Components, Methodology, and Implementations

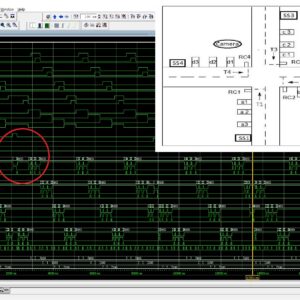

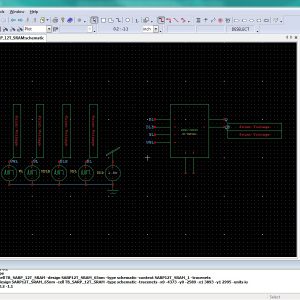

Scalable JTAG-Based 32-Bit Memory Test Architecture with MATS+ and MATS++/March-C Fault Detection

Smart Intelligent and Adaptive Traffic Controller using FPGA

Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability for Aerospace Applications

Soft-Error-Aware SRAM with Multinode Upset Tolerance for Aerospace Applications

Sparse FIR Filter Design via Partial 1-Norm Optimization

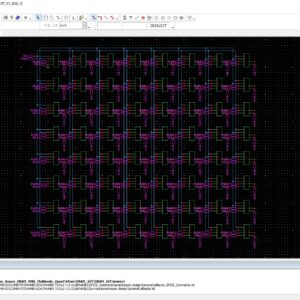

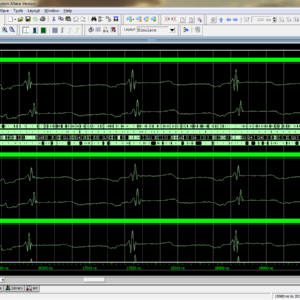

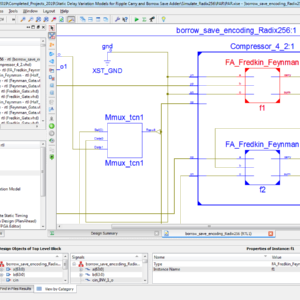

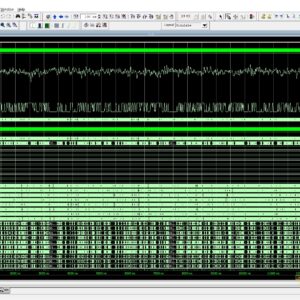

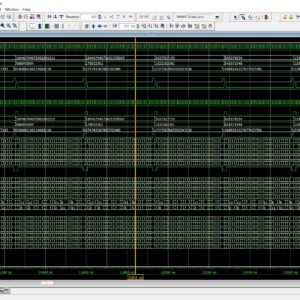

Static Delay Variations Modules For Ripple-Carry and Borrow Save Adders

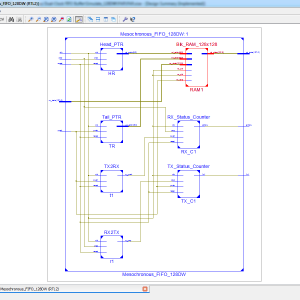

The Mesochronous Dual-Clock FIFO Buffer

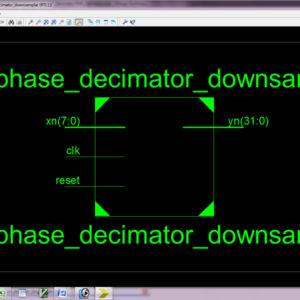

To develop and Implement Low Power, High Speed VLSI for Processing Signals using Multi rate Techniques Low Power Divider Using Vedic Mathematics

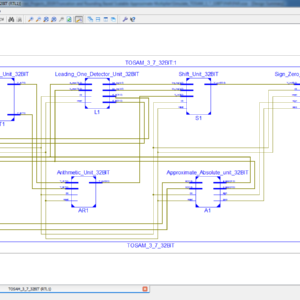

TOSAM: An Energy-Efficient Truncation- and Rounding-Based Scalable Approximate Multiplier

Toward the Multiple Constant Multiplication at Minimal Hardware Cost

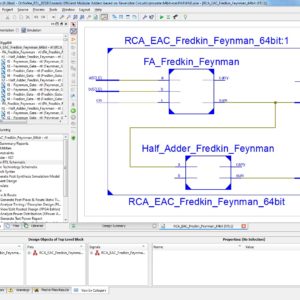

Towards Efficient Modular Adders based on Reversible Circuits

Two Efficient Approximate Unsigned Multipliers by Developing New Configuration for Approximate 4:2 Compressors

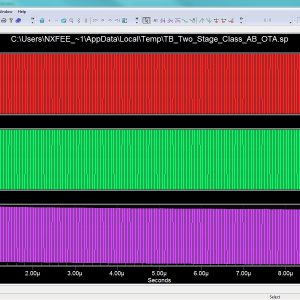

Two-Stage OTA With All Subthreshold MOSFETs and Optimum GBW to DC-Current Ratio

Ultra Lightweight Cryptography: Exploring the Application and Optimization of the PRESENT Cipher

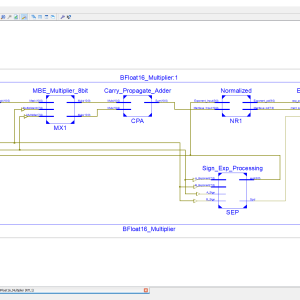

Variable-Precision Approximate Floating-Point Multiplier for Efficient Deep Learning Computation

Vital-Sign Processing Receiver With Clutter Elimination Using Servo Feedback Loop for UWB Pulse Radar System

VLSI Design of SVM-Based Seizure Detection System With On-Chip Learning Capability

World’s Fastest FFT Architectures: Breaking the Barrier of 100 GS/s

Provide Wordlwide Online Support

We can provide Online Support Wordlwide, with proper execution, explanation and additionally provide explanation video file for execution and explanations.

24/7 Support Center

NXFEE, will Provide on 24x7 Online Support, You can call or text at +91 9789443203, or email us nxfee.innovation@gmail.com

Terms & Conditions:

Customer are advice to watch the project video file output, and before the payment to test the requirement, correction will be applicable.

After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

Online support will not be given more than 3 times.

On first time explanation we can provide completely with video file support, other 2 we can provide doubt clarifications only.

If any Issue on Software license / System Error we can support and rectify that within end of day.

Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

After payment, to must send the payment receipt to our email id.

Powered by NXFEE INNOVATION, Pondicherry.

Call us today at : +91 9789443203 or Email us at nxfee.innovation@gmail.com

NXFEE Development & Services

Product Categories

- 2014 (11)

- 2015 (39)

- 2016 (30)

- 2017 (16)

- 2018 (17)

- 2019 (42)

- 2020 (29)

- 2021 (17)

- 2022 (23)

- Accessories (26)

- Area Efficient (114)

- High speed VLSI Design (54)

- IEEE (15)

- Image Processing (39)

- Low power VLSI Design (84)

- NOC VLSI Design (2)

- VLSI (231)

- VLSI 2023 (21)

- VLSI 2024 (15)

- VLSI 2025 (18)

- VLSI Application / Interface and Mini Projects (29)

- VLSI_2023 (15)

Filter by price

Product Status

Sort by producents

Copyright © 2026 Nxfee Innovation.