Seizure Prediction using Hilbert Huang Transform on Field Programmable Gate Array

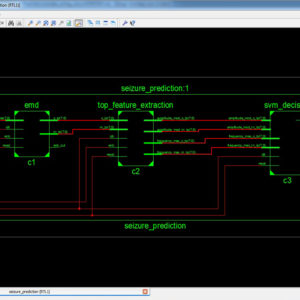

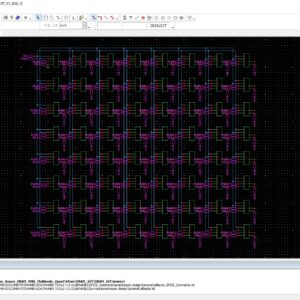

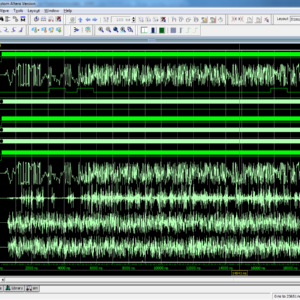

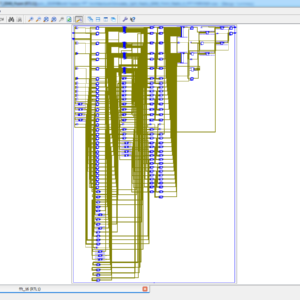

The Hilbert Huang Transform (HHT) has been used extensively in the time-frequency analysis of electroencephalography (EEG) signals and Brain-Computer Interfaces. Most studies utilizing the HHT for extracting features in seizure prediction have used intracranial EEG recordings. Invasive implants in the cortex have unknown long term consequences and pose the risk of complications during surgery. This added risk dimension makes them unsuitable for continuous monitoring as would be the requirement in a Body Area Network. We present an HHT based system on Field Programmable Gate Array (FPGA) for predicting epileptic seizures using scalp EEG. We use bandwidth features of Intrinsic Mode Functions and obtain a classification accuracy of close to 100% using patient-specific classifiers in software. Details of FPGA implementation are also given. The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2.

List of the following materials will be included with the Downloaded Backup:

Sharing Logic for Built In Generation of Functional Broadside Tests

Abstract: We are discussed about the built in generation for logic blocks. The advantage of this technique is identifying the similar characteristics of the each logical block. Functional broadside tests are important for addressing overtesting of delay faults as well as avoiding excessive power dissipation during test application. Finally to analysis the performance of the built in generation technique and compare to existing system.

List of the following materials will be included with the Downloaded Backup:Smart Intelligent and Adaptive Traffic Controller using FPGA

Proposed Abstract:

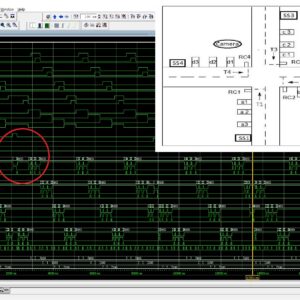

Traffic management is a critical aspect of modern urban infrastructure, and the ever-increasing volume of vehicles on the road demands innovative and adaptive solutions. This work presents a novel approach to traffic control using Field-Programmable Gate Arrays (FPGAs) as the core technology. The proposed system leverages the capabilities of FPGAs to create a Smart, Intelligent, and Adaptive Traffic Controller that can revolutionize urban traffic management. One of the key features of the proposed work is its adaptability. The system can dynamically adjust traffic signal timings and lane allocations in response to changing traffic patterns of 4-way road conditions with the help of sensor inputs. This methodology adaptability enhances road safety and minimizes traffic delays. The use of FPGA technology in the Traffic controller provides several advantages, including high computational performance, low power consumption, and the ability to reconfigure the system as traffic management needs evolve. Additionally, the system is highly scalable and can be deployed in various urban settings.

List of the following materials will be included with the Downloaded Backup:Soft-Error-Aware Read-Stability-Enhanced Low-Power 12T SRAM With Multi-Node Upset Recoverability for Aerospace Applications

Abstract:

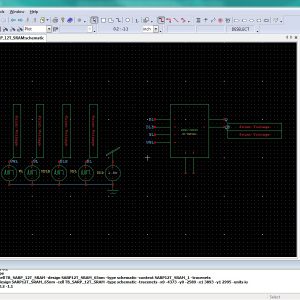

With the advancement of technology, the size of transistors and the distance between them are reducing rapidly. Therefore, the critical charge of sensitive nodes is reducing, making SRAM cells, used for aerospace applications, more vulnerable to soft-error. If a radiation particle strikes a sensitive node of the standard 6T SRAM cell, the stored data in the cell are flipped, causing a single-event upset (SEU). Therefore, in this paper, a Soft-Error-Aware Read-Stability-Enhanced Low Power 12T (SARP12T) SRAM cell is proposed to mitigate SEUs. To analyze the relative performance of SARP12T, it is compared with other recently published soft-error-aware SRAM cells, QUCCE12T, QUATRO12T, RHD12T, RHPD12T and RSP14T. All the sensitive nodes of SARP12T can regain their data even if the node values are flipped due to a radiation strike. Furthermore, SARP12T can recover from the effect of single event multi-node upsets (SEMNUs) induced at its storage node pair. Along with these advantages, the proposed cell exhibits the highest read stability, as the ‘0’-storing storage node, which is directly accessed by the bit line during read operation, can recover from any upset. Furthermore, SARP12T consumes the least hold power. SARP12T also exhibits higher write ability and shorter write delay than most of the comparison cells. All these improvements in the proposed cell are obtained by exhibiting only a slightly longer read delay and consuming slightly higher read and write energy.

List of the following materials will be included with the Downloaded Backup:Soft-Error-Aware SRAM with Multinode Upset Tolerance for Aerospace Applications

Base Paper Abstract:

As technology scales down, the critical charge (QC) of vulnerable nodes decreases, making SRAM cells more susceptible to soft errors in the aerospace industry. This article proposes a Soft-Error-Aware 16T (S8P8N) SRAM cell for aerospace applications to address this issue. The properties of S8P8N are evaluated and compared with 6T, DICE, QUCCE12T, WEQUATRO, RHBD10T, RHBD12T, S4P8N, SEA14T, and SRRD12T. Simulation results indicate that all vulnerable nodes and key node pairs of the proposed cell can recover to their original states when affected by a soft error. Additionally, it can recover from key multinode upsets. The write speed of the proposed cell is found to be reduced by 20.3%, 50.1%, 74.1%, 63.7%, and 50.41% compared to 6T, DICE, QUCCE12T, WEQUATRO, and RHBD10T, respectively. The read speed of the proposed cell is found to be reduced by 56.6%, 52.2%, 62.5%, and 35.2% compared to 6T, SRRD12T, RHBD12T, and S4P8N, respectively. It also shows that the hold power of the proposed cell is found to be reduced by 14.1%, 13.8%, 17.7%, and 23.4% compared to DICE, WEQUATRO, RHBD10T, and RHBD12T. Furthermore, the read static noise margin (RSNM) of the proposed cell is found to be enhanced by 157%, 67%, and 32% compared to RHBD12T, SEA14T, and SRRD12T. All these improvements are achieved with a slight area penalty.

List of the following materials will be included with the Downloaded Backup:Source Code Error Detection in High Level Synthesis Functional Verification

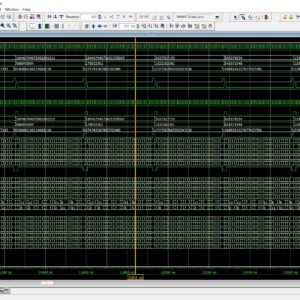

A dynamic functional verification method that compares untimed simulations versus timed simulations for synthesizable [high-level synthesis (HLS)] behavioral descriptions (ANSI-C) is presented in this paper. This paper proposes a method that automatically inserts a set of probes into the untimed behavioral description. These probes record the status of internal signals of the behavioral description during an initial untimed simulation. These simulation results are subsequently used as golden outputs for the verification of the internal signals during a timed simulation once the behavioral description has been synthesized using HLS. Our proposed method reports any simulation mismatches and accurately pinpoints any discrepancies between the functional Software (SW) simulation and the timed simulation at the original behavioral description (source code). Our method does not only determine where to place the probes, but is also able to insert different type of probes based on the specified HLS synthesis options in order not to interfere with the HLS process, minimizing the total number of probes and the size of the data to be stored in the trace file in order to minimize the running time. Results show that our proposed method is very effective and extremely simple to use as it is fully automated using Xilinx 14.2.

List of the following materials will be included with the Downloaded Backup:

Sparse FIR Filter Design via Partial 1-Norm Optimization

Abstract:

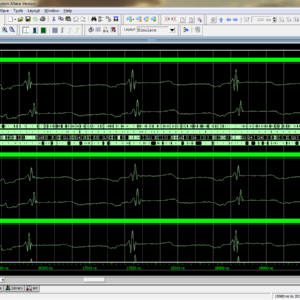

Electrocardiogram (ECG) is a form of cardiovascular measurement, for the diagnosis of different heart rate conditions. However, numerous noises usually harm the amplitude and time period of the signal from the ECG signal, at following a transition of the analog ECG signal from the sensor module into a digital format. The appropriate digital filter may be used to remove different forms of noise such as Baseline Wander, Power line interference, High frequency noise and Physiological Artifacts. The Digital FIR filter will have prospected to reduced the artifacts in the ECG signals. The signals taken from the MIT-BIH data base which contains the normal and abnormal waveforms. This Digital FIR filter can have more performance by using more TAP numbers such as multiplying, delaying and getting more effectiveness. This proposed work would implement a 1 norm minimization in the FIR filter with liner step method to minimize sparse complexity and reduce the mini-max approximation error for sparse maximization. Given these facts, several rules for selecting indicators of potential zero coefficients to be used in 1 standard optimization are adopted in the proposed algorithm. The efficacy of the proposed design algorithm was developed in Verilog HDL, simulated in Modelsim software and synthesized in Xilinx vertex 5 FPGA, and finally prove all the parameters in terms of area, delay and power.

List of the following materials will be included with the Downloaded Backup:Static Delay Variations Modules For Ripple-Carry and Borrow Save Adders

Abstract:

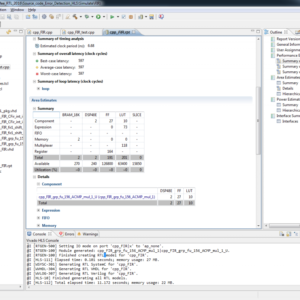

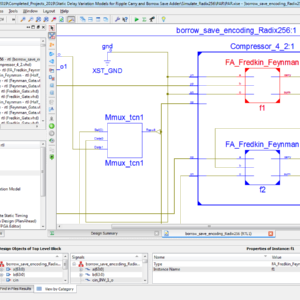

This paper introduces two statistical delay variability models for certain hardware adder implementations, namely, the ripple-carry adder (RCA) and the borrow-save adder (BSA). The introduced models take into account correlated variation sources. Initially, we derive a first proposed model, namely, Type-I model, in the form of expressions for the computation of the exact Probability Density Functions (PDFS) of maximum output delays for Gaussian and non-Gaussian variation sources. Furthermore, we present closed formulas for the co-variances between output delays of the aforementioned adder architectures. The introduced derived co-variances are subsequently combined with Clark’s method to derive a second proposed model, Type-II model, which comprises approximations of the maximum delay PDF for an RCA and a BSA. Simulation results and the derived exact Type-I PDFs are found to perfectly agree, while the proposed Clark-based Type-II models present an error for standard deviation of maximum delay that increases as BSA word length increases. Both the introduced models and the simulations prove that BSAs achieve narrower delay distributions than RCAs, i.e., they significantly reduce delay variance. Consequently, BSAs are proven to be suitable for variation-tolerant applications by providing a timing safety margin, when compared to RCA architectures. The underlying analysis indicates that for the case of BSA and either intra-die delay variations only or both intra and inter-die delay variations, the Type-II models introduce non negligible errors, which are as much as 16% of the standard deviation of maximum delay for a 256-digit BSA, as the Type II Gaussian PDF approximations deviate significantly from the exact Type-I PDFs. However, for all RCA and BSA inter-die only variation cases, both types present satisfactory accuracy due to the Gaussian shape of exact PDF.

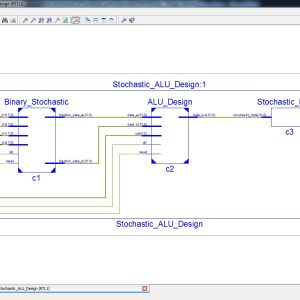

List of the following materials will be included with the Downloaded Backup:Stochastic Implementation and Analysis of Dynamical Systems Similar to the Logistic Map

Abstract:

Stochastic computing (SC) is a digital computation approach that operates on random bit streams to perform complex tasks with much smaller hardware, with compared to conventional binary radix approaches. It is characterized by its use of pseudo-random numbers implemented by 0-1 sequences called stochastic numbers (SN) are interpreted as probabilities. Accuracy is usually assumed to depend on the interacting SN being highly independent or uncorrelated in a loosely specified way. This paper introduced a new approach of Stochastic and Analysis of Dynamical digital computation with ALU Design. In existing comparison of Floating point ALU Design is not implemented a Stochastic approach, So here the proposed will design to implemented a Stochastic Computing in ALU Design. In top-down design approach of ALU Design, four arithmetic modules, addition, subtraction, multiplication and division are combined to form a Stochastic ALU Unit. Each module is divided into sub-module with two selection bits are combined to select a particular operation. Each module is independent to each other. This modules are realized and validated using VHDL simulation and synthesized in Xilinx 14.2, finally shown the comparison of Area, Power and Delay.

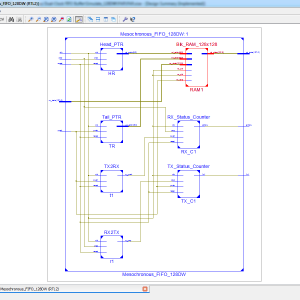

List of the following materials will be included with the Downloaded Backup:The Mesochronous Dual-Clock FIFO Buffer

Abstract:

To increase system composability and facilitate timing closure, fully synchronous clocking is replaced by more relaxed clocking schemes, such as mesochronous clocking. Under this regime, the modules at the two ends of a mesochronous interface receive the same clock signal, thus operating under the same clock frequency, but the edges of the arriving clock signals may exhibit an unknown phase relationship. In such cases, clock synchronization is needed when sending data across modules. In this brief, we present a novel mesochronous dual-clock first-input– first-output (FIFO) buffer that can handle both clock synchronization and temporary data storage, by synchronizing data implicitly through the explicit synchronization of only the flow-control signals. The proposed design can operate correctly even when the transmitter and the receiver are separated by a long link whose delay cannot fit within the target operating frequency. In such scenarios, the proposed mesochronous FIFO can be extended to support multicycle link delays in a modular manner and with minimal modifications to the baseline architecture. When compared with the other state-of-the-art dual-clock mesochronous FIFO designs, the new architecture is demonstrated to yield a substantially lower cost implementation.

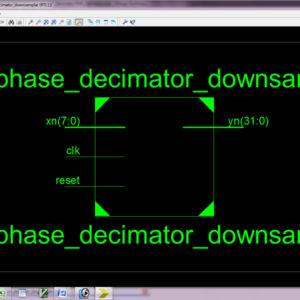

List of the following materials will be included with the Downloaded Backup:To develop and Implement Low Power, High Speed VLSI for Processing Signals using Multi rate Techniques Low Power Divider Using Vedic Mathematics

Abstract:

Multirate technique is necessary for systems with different input and output sampling rates. Recent advances in mobile computing and communication applications demand low power and high speed VLSI DSP systems. In this paper to discuss the downsampling technique and its improvement, major drawbacks of present approaches possible to increase degeneracy. This Multirate design methodology is systematic and applicable to many problems. The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2.The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2.

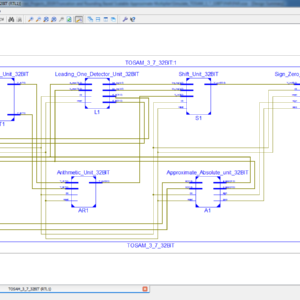

List of the following materials will be included with the Downloaded Backup:TOSAM: An Energy-Efficient Truncation- and Rounding-Based Scalable Approximate Multiplier

Abstract:

A scalable approximate multiplier, called truncation- and rounding-based scalable approximate multiplier (TOSAM) is presented, which reduces the number of partial products by truncating each of the input operands based on their leading one-bit position. In the proposed design, multiplication is performed by shift, add, and small fixed-width multiplication operations resulting in large improvements in the energy consumption and area occupation compared to those of the exact multiplier. To improve the total accuracy, input operands of the multiplication part are rounded to the nearest odd number. Because input operands are truncated based on their leading one-bit positions, the accuracy becomes weakly dependent on the width of the input operands and the multiplier becomes scalable. Higher improvements in design parameters (e.g., area and energy consumption) can be achieved as the input operand widths increase. To evaluate the efficiency of the proposed approximate multiplier, its design parameters are compared with those of an exact multiplier and some other recently proposed approximate multipliers. Results reveal that the proposed approximate multiplier with a mean absolute relative error in the range of 11%–0.3% improves delay, area, and energy consumption up to 41%, 90%, and 98%, respectively, compared to those of the exact multiplier. It also outperforms other approximate multipliers in terms of speed, area, and energy consumption. The proposed approximate multiplier has an almost Gaussian error distribution with a near-zero mean value. We exploit it in the structure of a JPEG encoder, sharpening, and classification applications. The results indicate that the quality degradation of the output is negligible. In addition, we suggest an accuracy configurable TOSAM where the energy consumption of the multiplication operation can be adjusted based on the minimum required accuracy.

List of the following materials will be included with the Downloaded Backup:Toward the Multiple Constant Multiplication at Minimal Hardware Cost

Base Paper Abstract:

Multiple Constant Multiplication (MCM) over integers is a frequent operation arising in embedded systems that require highly optimized hardware. An efficient way is to replace costly generic multiplication by bit-shifts and additions, i. e. a multiplier less circuit. In this work, we improve the state of-the-art optimal approach for MCM, based on Integer Linear Programming (ILP). We introduce a new low-level hardware cost metric, which counts the number of one-bit adders and demonstrate that it is strongly correlated with the LUT count. This new model permitted us to consider intermediate truncations that permit to significantly save resources when a full output precision is not required. We incorporate the error propagation rules into our ILP model to guarantee a user-given error bound on the MCM results. The proposed ILP models for multiple flavors of MCM are implemented as an open-source tool and, combined with an automatic code generator, provide a complete coefficient-to-VHDL flow. We evaluate our models in extensive experiments, and propose an in-depth analysis of the impact that design metrics have on synthesized hardware.

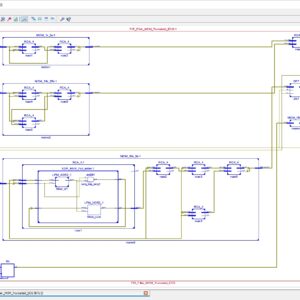

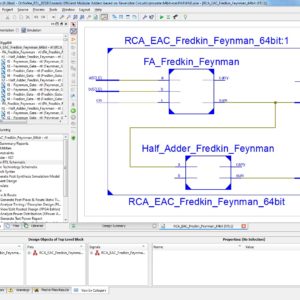

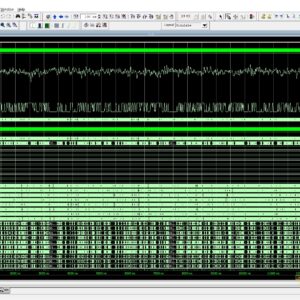

List of the following materials will be included with the Downloaded Backup:Towards Efficient Modular Adders based on Reversible Circuits

Abstract:

Reversible logic is a computing paradigm that has attracted significant attention in recent years due to its properties that lead to ultra-low power and reliable circuits. Reversible circuits are fundamental, for example, for quantum computing. Since addition is a fundamental operation, designing efficient adders is a cornerstone in the research of reversible circuits. Residue Number Systems (RNS) has been as a powerful tool to provide parallel and fault-tolerant implementations of computations where additions and multiplications are dominant. In this paper, for the first time in the literature, we propose the combination of RNS and reversible logic. The parallelism of RNS is leveraged to increase the performance of reversible computational circuits. Being the most fundamental part in any RNS, in this work we propose the implementation of modular adders, namely modulo 2n-1 adders, using reversible logic. Analysis and comparison with traditional logic show that modulo adders can be designed using reversible gates with minimum overhead in comparison to regular reversible adders.

List of the following materials will be included with the Downloaded Backup:Two Efficient Approximate Unsigned Multipliers by Developing New Configuration for Approximate 4:2 Compressors

Base Paper Abstract:

Approximate computing is a promising approach for reducing power consumption and design complexity in applications that accuracy is not a crucial factor. Approximate multipliers are commonly used in error-tolerant applications. This paper presents three approximate 4:2 compressors and two approximate multiplier designs, aiming at reducing the area and power consumption, while maintaining acceptable accuracy. The paper seeks to develop approximate compressors that align positive and negative approximations for input patterns that have the same probability. Additionally, the proposed compressors are utilized to construct approximate multipliers for different columns of partial products based on the input probabilities of the two compressors in adjacent columns. The proposed approximate multipliers are synthesized using the 28nm technology. Compared to the exact multiplier, the first proposed multiplier improves power × delay and area × power by 91% and 86%, respectively, while the second proposed multiplier improves the two parameters by 90% and 84%, respectively. The performance of the proposed approximate methods was assessed and compared with the existing methods for image multiplication, sharpening, smoothing and edge detection. Also, the performance of the proposed multipliers in the hardware implementation of the neural network was investigated, and the simulation results indicate that the proposed multipliers have appropriate accuracy in these applications.

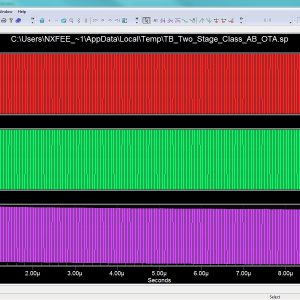

List of the following materials will be included with the Downloaded Backup:Two-Stage OTA With All Subthreshold MOSFETs and Optimum GBW to DC-Current Ratio

Base Paper Abstract:

An approach for the design of two-stage class AB OTAs with sub-1µA current consumption is proposed and demonstrated. The approach employs MOS transistors operating in subthreshold and allows maximum gain-bandwidth product (GBW) to be achieved for a given DC current budget, by setting optimum distribution of DC currents in the two amplifier stages. Following this strategy, a class AB OTA was designed in a standard 0.5-µm CMOS technology supplied from 1.6-V and experimentally tested. Measured GBW was 307 kHz with 980-nA DC current consumption while driving an output capacitance of 40 pF with an average slew rate of 96 V/ms.

List of the following materials will be included with the Downloaded Backup:Ultra Lightweight Cryptography: Exploring the Application and Optimization of the PRESENT Cipher

Proposed Abstract:

The PRESENT cipher, an ultra-lightweight block cipher, has been designed specifically for environments where resource constraints are a critical factor, such as RFID tags, sensor networks, and various IoT devices. Its compact design, featuring a 64-bit block size, 80-bit key, and 31 rounds, makes it particularly suitable for applications requiring minimal hardware resources, low power consumption, and moderate security. Unlike more robust ciphers like AES, which demand significant computational and memory resources, PRESENT strikes an optimal balance between efficiency and security for constrained devices. This paper explores the practical applications of the PRESENT cipher in secure communication protocols, device authentication, and data encryption in low-power systems. By synthesizing 16-bit, 32-bit, and 64-bit implementations on a Xilinx Virtex-5 FPGA, we demonstrate the cipher’s adaptability across a range of use cases, analyzing key performance metrics such as area, delay, and power consumption. Our findings indicate that PRESENT is highly effective in scenarios where traditional cryptographic solutions are too resource-intensive, offering a viable alternative for securing data in pervasive computing environments. PRESENT’s applications extend to securing communication in embedded systems, protecting sensitive information in contactless payment systems, and enabling secure data transmission in wireless sensor networks. The cipher’s lightweight design ensures that it can be implemented in devices with limited processing capabilities, making it an ideal choice for modern IoT applications. However, the trade-off between security and efficiency must be carefully considered. While PRESENT is suitable for applications with moderate security requirements, it may not provide the level of protection needed for high-security environments.

List of the following materials will be included with the Downloaded Backup:Variable-Precision Approximate Floating-Point Multiplier for Efficient Deep Learning Computation

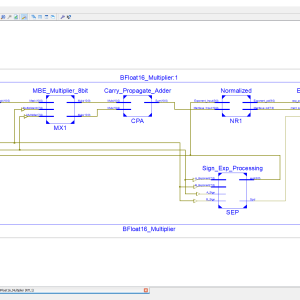

Base Paper Abstract:

In this brief, a variable-precision approximate floating-point multiplier is proposed for energy efficient deep learning computation. The proposed architecture supports approximate multiplication with BFloat16 format. As the input and output activations of deep learning models usually follow normal distribution, inspired by the posit format, for numbers with different values, different precisions can be applied to represent them. In the proposed architecture, posit encoding is used to change the level of approximation, and the precision of the computation is controlled by the value of product exponent. For large exponent, smaller precision multiplication is applied to mantissa and for small exponent, higher precision computation is applied. Truncation is used as approximate method in the proposed design while the number of bit positions to be truncated is controlled by the values of the product exponent. The proposed design can achieve 19% area reduction and 42% power reduction compared to the normal BFloat16 multiplier. When applying the proposed multiplier in deep learning computation, almost the same accuracy as that of normal BFloat16 multiplier can be achieved.

List of the following materials will be included with the Downloaded Backup:Vital-Sign Processing Receiver With Clutter Elimination Using Servo Feedback Loop for UWB Pulse Radar System

Abstract:

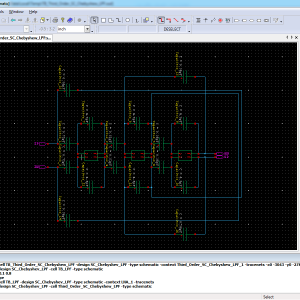

This brief presents a vital-sign processing circuit for simultaneous dc/near-dc elimination and out-of-band interference rejection without any digital signal processing or algorithm assistance for the ultra wideband (UWB) pulse-based radar system. An intrinsic self balanced MOS diode (SBMD) was proposed as a stable and balanced pseudo resistor applied under a servo feedback loop in a vital-sign receiver of the sensing radar to perform as a high-pass filter (HPF) with an ultralow corner frequency lower than 0.5 Hz for removing undesired clutters of the reflected signals and input dc-offset voltages from innate circuit offsets. A third-order switched-capacitor (SC) Chebyshev low-pass filter (LPF) with leap-frog topology as the subsequent stage was adopted to suppress the out-band noises, thereby establishing an integrated vital-sign processing circuit with band pass frequency response and incorporating it into a radar module to verify its viability.

List of the following materials will be included with the Downloaded Backup:VLSI Design of SVM-Based Seizure Detection System With On-Chip Learning Capability

Abstract:

Portable automatic seizure detection system is very convenient for epilepsy patients to carry. In order to make the system on-chip trainable with high efficiency and attain high detection accuracy, this paper presents a very large scale integration (VLSI) design based on the nonlinear support vector machine (SVM). The proposed design mainly consists of a feature extraction (FE) module and an SVM module. The FE module performs the three level Daubechies discrete wavelet transform to fit the physiological bands of the electroencephalogram (EEG) signal and extracts the time–frequency domain features reflecting the non stationary signal properties. The SVM module integrates the modified sequential minimal optimization algorithm with the table-driven-based Gaussian kernel to enable efficient on-chip learning. The presented design is verified on an Altera Cyclone II field-programmable gate array and tested using the two publicly available EEG datasets. Experiment results show that the designed VLSI system improves the detection accuracy and training efficiency.

List of the following materials will be included with the Downloaded Backup:VLSI Implementation of an Edge-Oriented Image Scaling Processor

Abstract:

Image scaling is a very important technique and has been widely used in many image processing applications. In this paper, we present an edge-oriented area-pixel scaling processor. To achieve the goal of low cost, the area-pixel scaling technique is implemented with a low-complexity VLSI architecture in our design. A simple edge catching technique is adopted to preserve the image edge features effectively so as to achieve better image quality. Compared with the previous low-complexity techniques, our method performs better in terms of both quantitative evaluation and visual quality. The seven-stage VLSI architecture of our image scaling processor contains 10.4-K gate counts and yields a processing rate of about 200 MHz by using TSMC 0.18- m technology.

List of the following materials will be included with the Downloaded Backup:VLSI Implementation of Efficient Image Watermarking Algorithm

Abstract:

The watermarking is the important multimedia content for authentication and security in nowadays. We are proposed to implement the watermarking in FPGA with VLSI architecture. And also use the Haar discrete wallet transform and bit plane slicing for creating the water marking images and extracted watermark images. The area, power, delay of the proposed architecture is analysis using Xilinx 14.2.

List of the following materials will be included with the Downloaded Backup:VLSI-Oriented Lossy Image Compression Approach using DA-Based 2D-Discrete Wavelet

We introduced a Discrete Wavelet Transform (DWT) based VLSI-oriented lossy image compression approach, widely used as the core of digital image compression. Here, Distributed Arithmetic (DA) technique is applied to determine the wavelet coefficients, so that the number of arithmetic operation can be reduced substantially. As well, the compression rate is enhanced with the aid of introducing RW block that blocks some of the coefficients obtained from the high pass filter to zero. Subsequently, Differential Pulse-Code Modulation (DPCM) and huffman-encoding are applied to acquire the binary sequence of the image. The proposed architecture of this paper analysis the logic size, area and power consumption using Xilinx 14.2.

List of the following materials will be included with the Downloaded Backup:World’s Fastest FFT Architectures: Breaking the Barrier of 100 GS/s

Abstract:

This paper presents the fastest fast Fourier transform (FFT) hardware architectures so far. The architectures are based on a fully parallel implementation of the FFT algorithm. In order to obtain the highest throughput while keeping the resource utilization low, we base our design on making use of advanced shift-and-add techniques to implement the rotators and on selecting the most suitable FFT algorithms for these architectures. Apart from high throughput and resource efficiency, we also guarantee high accuracy in the proposed architectures. For the implementation, we have developed an automatic tool that generates the architectures as a function of the FFT size, input word length and accuracy of the rotations. We provide experimental results covering various FFT sizes, FFT algorithms, and field-programmable gate array boards. These results show that it is possible to break the barrier of 100 GS/s for FFT calculation.

List of the following materials will be included with the Downloaded Backup:Provide Wordlwide Online Support

We can provide Online Support Wordlwide, with proper execution, explanation and additionally provide explanation video file for execution and explanations.

24/7 Support Center

NXFEE, will Provide on 24x7 Online Support, You can call or text at +91 9789443203, or email us nxfee.innovation@gmail.com

Terms & Conditions:

Customer are advice to watch the project video file output, and before the payment to test the requirement, correction will be applicable.

After payment, if any correction in the Project is accepted, but requirement changes is applicable with updated charges based upon the requirement.

After payment the student having doubts, correction, software error, hardware errors, coding doubts are accepted.

Online support will not be given more than 3 times.

On first time explanation we can provide completely with video file support, other 2 we can provide doubt clarifications only.

If any Issue on Software license / System Error we can support and rectify that within end of day.

Extra Charges For duplicate bill copy. Bill must be paid in full, No part payment will be accepted.

After payment, to must send the payment receipt to our email id.

Powered by NXFEE INNOVATION, Pondicherry.

Call us today at : +91 9789443203 or Email us at nxfee.innovation@gmail.com

NXFEE Development & Services

Copyright © 2026 Nxfee Innovation.